ジッタ・クリーナを調べてみる! の巻き 2011.9.11

ことのきっかけはこのメールをいただいたことから始まりました。

|

おもしろそうです。ジッタを除去するIC?なんだろう? とても興味が沸いてきます。

なにやらジッタを数100fs(フェムト秒)単位まで追い込むもののようです。

CS8416のジッタが200ps、ジッタの少ないDIR9001ですら75psですからおよそ1/1000程度に

ジッタが抑えられます。一般の低ジッタとよばれる水晶発振器でも数psのオーダですから、

それより1/10-1/100ほどよいことになります。これがつかえたら面白いかもです。

他のメーカは?

まずは、ほかに出しているメーカは無いか調べてみました。キーワードはジッタクリーナというものです。

ご紹介いただいたICはSilicon Laboratories Incのものですが、

DIGIKEYの検索ページでJitter Cleanerでしらべると、3社ほどみつかりました。

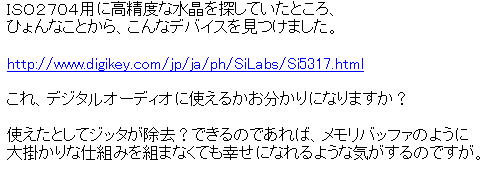

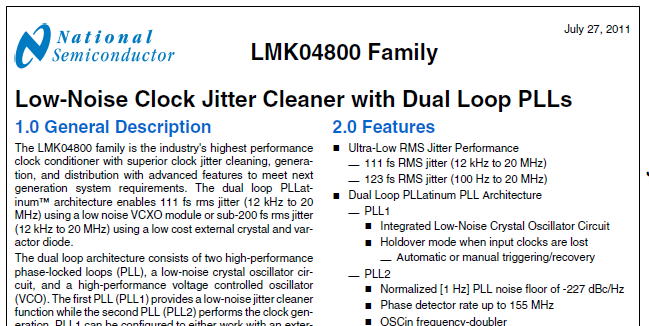

1つはNS社のものです。こちらは111fsのジッタを謳ってますね。

でもちょっと足が多いし、マニュアルをみてみるとマイコン制御が必要になりそうです。

|

|

|

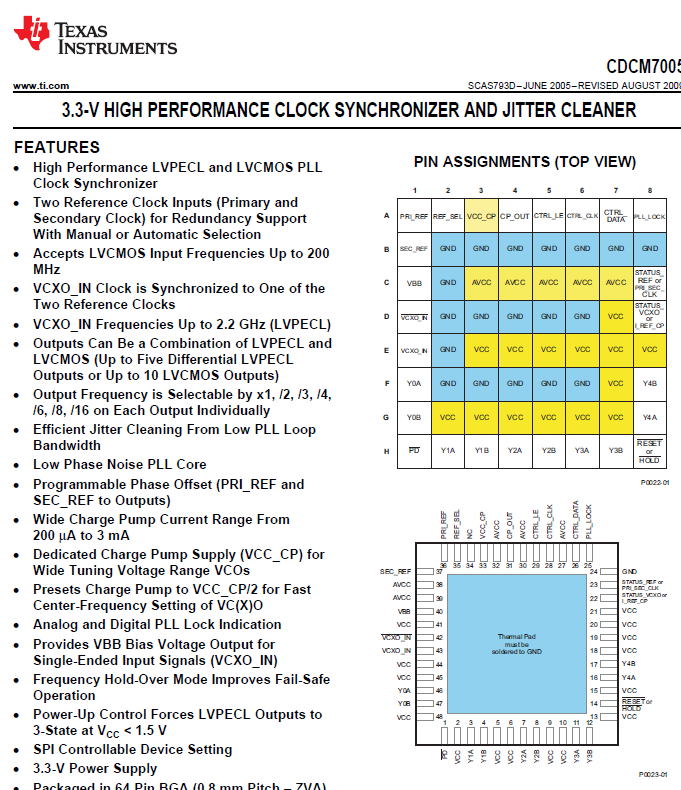

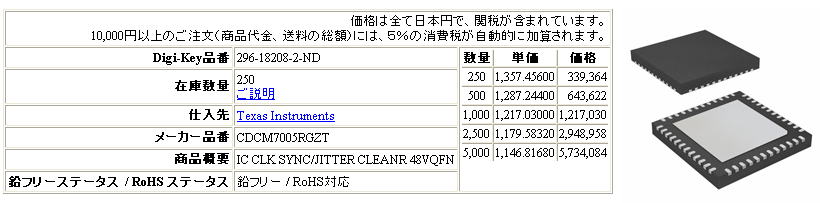

2つ目はTI社のもの。こちらも足が多いです。周波数帯も1.5GHzまでつかるようなのですが、

こちらもマイコン制御が必要なようです。

|

|

|

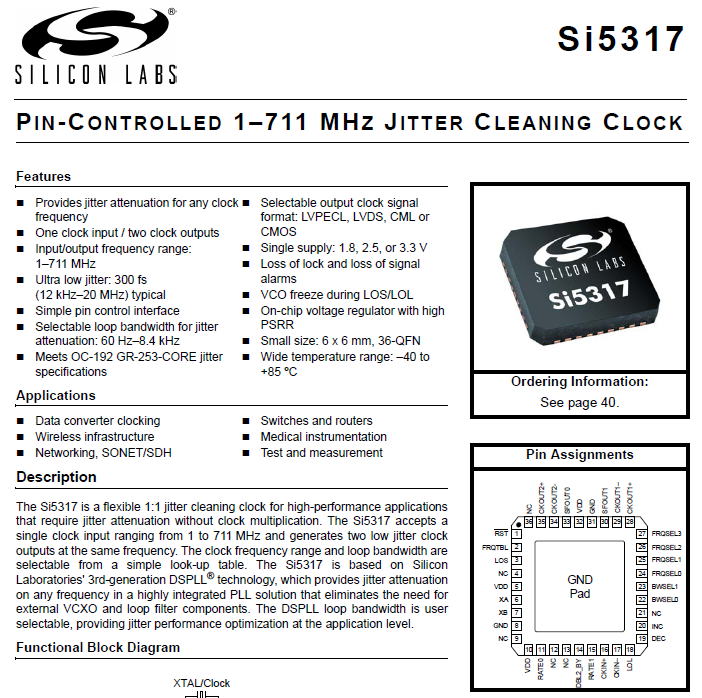

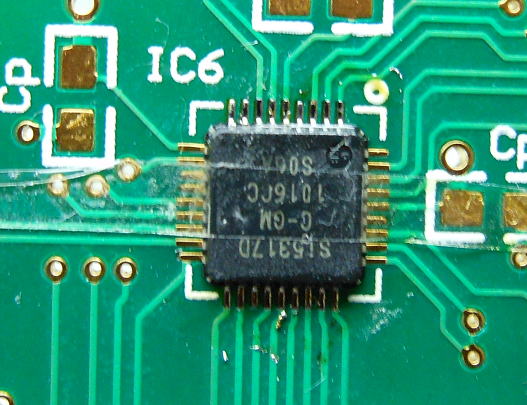

こちらは紹介いただいたSi5317です。

足の数も少ないです。うれしいのはマイコン制御ではなくハードウエアによるピン設定でモードがいろいろと変えられる点です。

マイコンを使わないと、チェックのトラブルが少なくなるのでうれしいです(反面、ハードだと設定の面倒さが顕在化することも多々ある)。

|

|

|

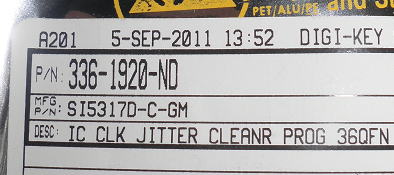

とりあえず購入!

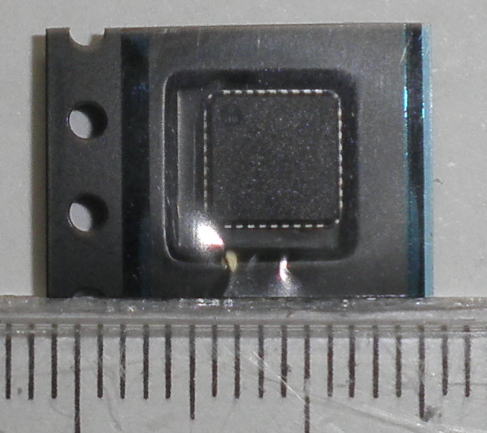

それほど高いICではないのでSi5317を1つ購入してみました。このパッケージ(PLCC)を使うのは初めてです。

まずは変換基板から探さなくっちゃ! そしてマニュアルも良く読みましょう。

ちなみにマニュアルはここに入れておきます。

とりあえずいつものDIGIKEYから調達です。部品箱の肥やしにならなかったらいいのですが・・・・

買ってみたものはいいけれど・・・・ 2011.9.12

どのように使うのが効果的かな?そもそもどのクロックに適用すればいいのだろう?

考えられるパターンはいくつか列挙すると

1.ASRCのPLL1708出力に入れる

これは効果抜群のような気がします。PLL1708は低ジッタですが、それでも50psあります。

このSi5317をいれることで2桁から3桁近くジッタが改善することになります。ただし、SPDIF出力にすると

DAIで受けたPLLでジッタが再発生するので、ASRCの3線制御出力が直接DACにつながっている必要があるかも

しれません。

2.(Renew)DAC1704のBCKラインに挿入

これもいいかもしれません。BCKをはすべての動作の基本クロックですから、これの精度を上げるのは

効果あるでしょう。ただし、送り手がすでにメモリーバッファーなどの場合は、効果がすこし薄まるかもです

(それでも1桁くらいはジッタ性能があがることが期待できるかも・・・・搭載されるクロックに依存ですね)。

ただし、気になるのはジッタクリーナに入力されるクロックの位相と出力の位相は同じなのだろうか?

3.DAIのシステムクロックをクリーナする。

これは原理的に効果あるのだろうか?システムクロックは内部の演算処理に必要なクロックを提供しているだけと

認識しているのだけど、やはりシステムクロックではなくBCKをクリーナしたほうがいいのかな?

いづれにしても、上記の1以外への用途については、クロックの入力と出力の位相差がどうなるかが気になるところです。

マニュアルを読めばでてくるのかな?それとも実験しないとわからないかな?

位相差は調整できそう 2011.9.14

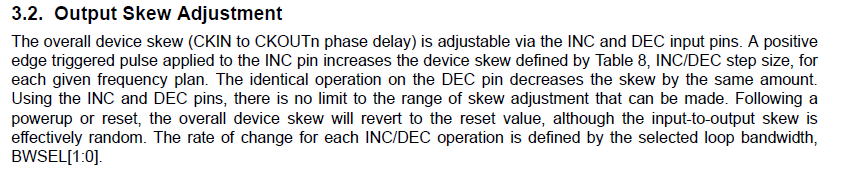

マニュアルを読み進めていると、位相差の調整はできそうです。

スキュー調整でおこなうみたいでSi5317のINC/DEC端子にパルスをたたき込むことで位相差は調整できそうです。

|

ただし、1回のパルスで調整できる量はおおむね0.2nsです。ということは10MHzのクロックなら

1周期ずらすには100ns/0.2ns=500パルスは必要になるということです。

こりやマニュアルでの調整は大変です。

それと位相差を調べる手立てが必要です。

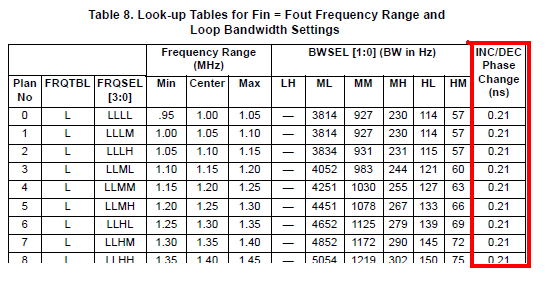

位相差を検知するには

位相差を調べるのはそれほど難しくはありません。

7474などのD-FF(フリップフロップ)が1回路あれば、位相が進んでいるのか遅れているのかの区別がつきます。

この回路はメモリーバッファーのビートチェッカでつかったものと同じ考え方です。

位相差の検知方法。これは比較的簡単

では位相差量を調べるにはどうするか?これもEX-ORをつかって出力にLPFを構成しておいて、

AD変換で発生する電圧を調べれば位相差量が定量的にわかるのではと思っています。

位相差量の検知方法。EX-OR1個で簡単に実現できそうです。

ここまで考えられたら試作に一度動作させてみたいのですが、このICパッケージ(36QFN)の

変換基板が見あたりません。どうしよう?

評価基板を作るかな?

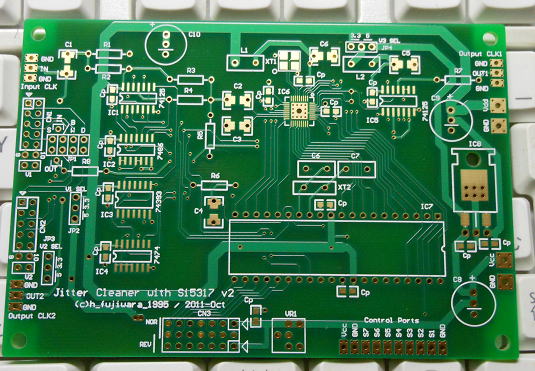

おもいきってパターンを書いてみました。IO設定数が多いのと、動作状態の確認できるようにマイコンと

液晶が接続できるようにしました。もちろん、位相差および位相差量の検知回路だけでなく、

自動的なパラメータ設定ができるようにと入力周波数を検知する機能も付加してみました。

といっても大げさなものではなく、入力信号を1/16あるいは1/256に分周してPICのカウンタに

接続するだけです。

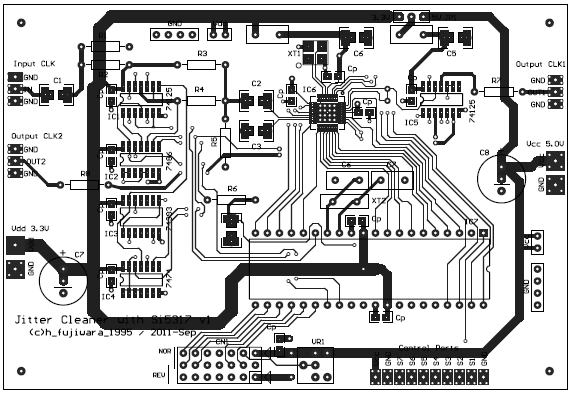

書いてみたパターン。今回は部品面を配線パタンとして半田面がベタ面です。

いつ作ろうかな?

とりあえず・・・・ 2011.9.19

試作基板は発注。10月頭には手にすることができるでしょう。それまでに、いろいろとソフトの構成を

考えておきましょう。

ありゃ・・・・ 2011.10.9

基板発注にミスがあったようで、結局納品になるのは来週になりそう・・・

とほほです。

基板到着 2011.10.13

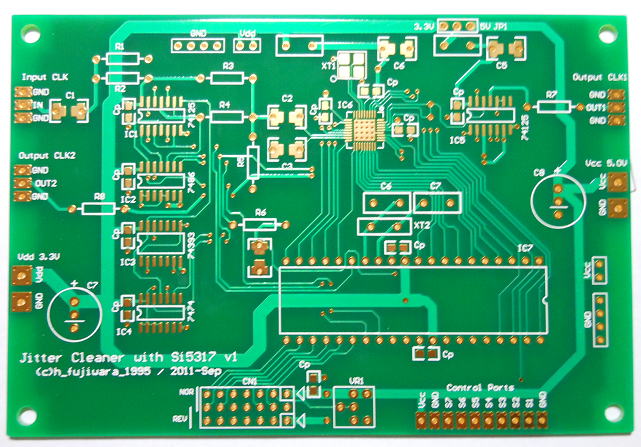

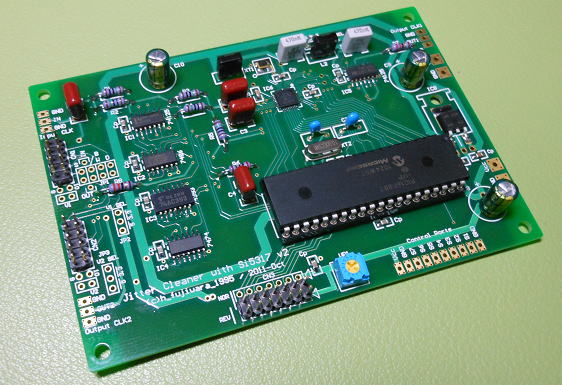

部品面です。

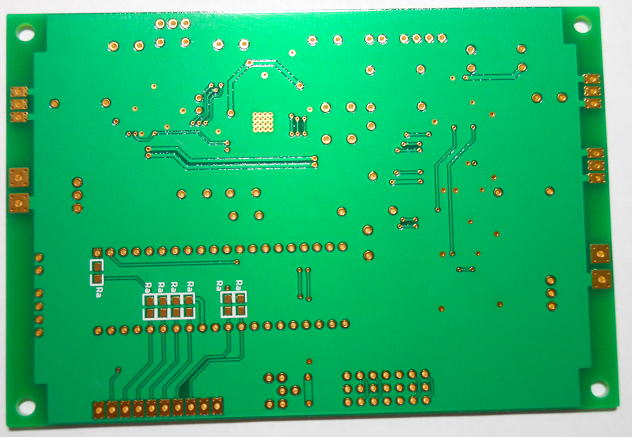

半田面です。こちらをベタにしました。

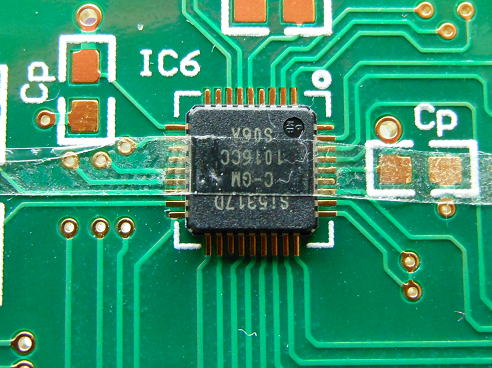

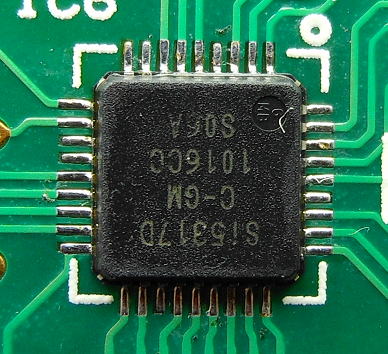

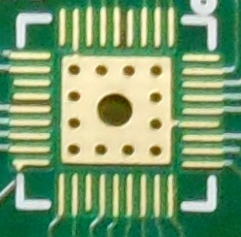

まずはSi5317の半田付け

半田付けは小さい部品から実装するのが王道です。

ということでSi5317から半田づけです。QFPパッケージなので4墨をあわせる必要があります。

細く切ったテープでまずは固定します。

固定したSi5317.

固定したらフラックスを塗って2面を半田付けします。そしたらテープをはがして、他方の2面を半田付けです。

QFPパッケージはブリッジがおこりにくいようなので案外簡単に半田付けできました。

2面を半田づけしたらテープを剥がして他方の2面を半田付けしします。

半田付けが終わったらディジカメやルーペで半田不良あるいはブリッジがないかよく確かめておきます。

大丈夫のようですね。

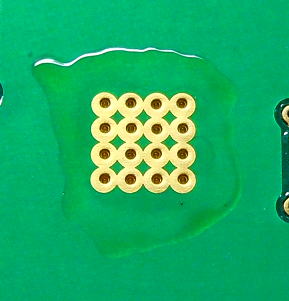

SI5317は発熱があるようなので裏面も半田パッドになっています。

ということで基板の裏面からも半田を流しこんで裏面と接合しておきまししょう。

裏面側からもたっぷり半田を流して接合しておきます。これが放熱に役立つのでしょう。

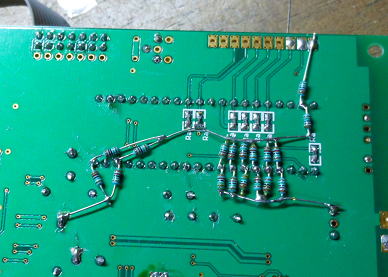

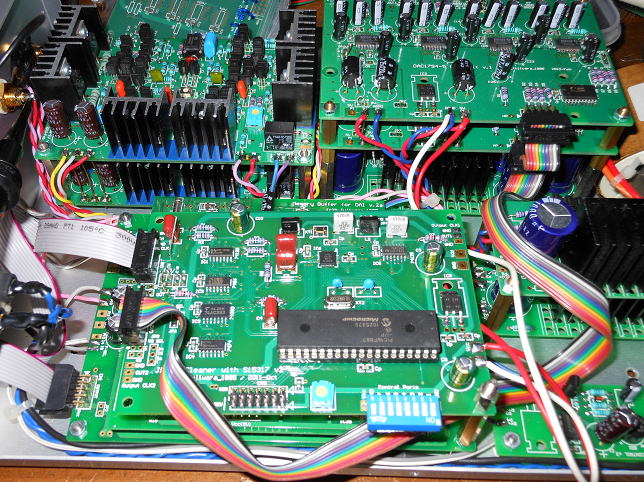

一気に全体をくみ上げました! 2011.10.15

試作だけあって、若干のパターン抜けやシルク抜けがありましたが、ご愛嬌です。

こんな感じで完成です。

ひさしぶりの作業再開! 2011.10.30

思い出したように作業再開です。半田付けだけは終了していたのですが、マイコンのプログラムができて

なくてようやく、動作に必要なコードを作成しました。

動かない・・・

電源をいれてみましたが、思ったように動きません。出力信号はでるのですが、全然入力信号にロックしません。

電圧を調べてみると、ちょっと違和感。もともとSI5317のロジック入力はL,Hに加えてMがあります。これは

IC内部でVDDとGNDにプルアップとプルダウンの両方が行われていて、開放時はMになるようになっています。

しかしMの範囲が結構狭く、0.45−0.55VDDとなっています。で、電圧を測ってみると1.85V程度あります。

3.3V動作ですから、0.56VDDとやや規格値をオーバーしている感じです。ということで、データシートにあるように

追加のプルアップ、プルダウン抵抗を実装しました。この場合の電圧は1.64Vになってほぼ中点電位になりました。

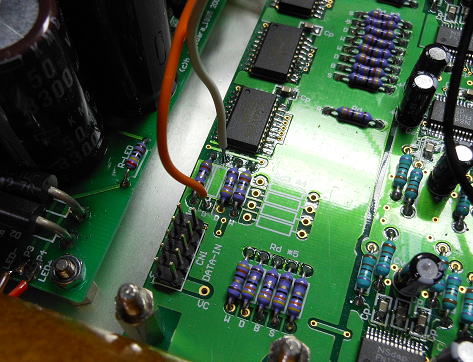

プルアップとプルダウン抵抗を追加しました。

動いた!

ここまでくれば、あとはソフトの調整だけです。

ソフトでは1-100MHzに自動的に対応するような機能と、入力と出力信号の位相差を

調整する機能を組み込みました。

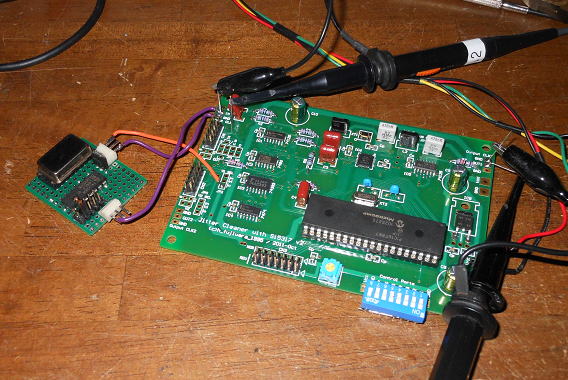

動作確認の様子です。

LCDは動作状態を示すようにしています。本来は不要なものです。

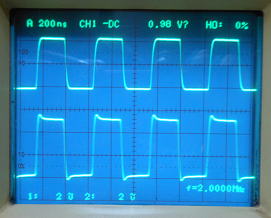

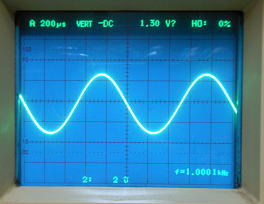

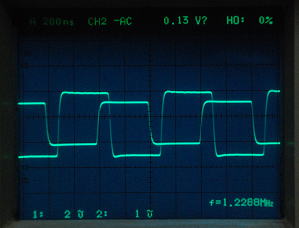

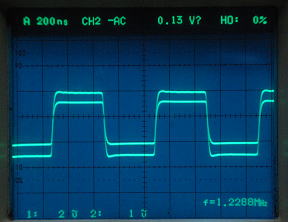

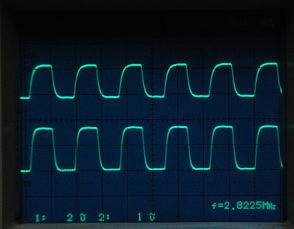

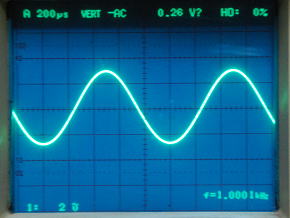

周波数ロックの様子。位相のばっちりあっています。(左:2MHz、右:6MHz)

下:入力信号 上:出力信号

ジッタ低減してるの?

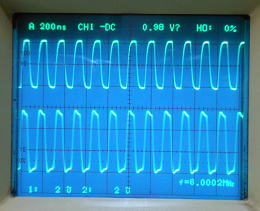

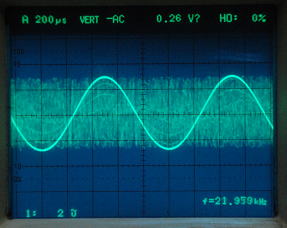

入力にはDDS発信機を使っていますが、高周波域ではジッタがでてきます。

これを利用してジッタが低減しているか調べてみましょう。

手元の20MHzのオシロではこの表示が限界ですが、Si5317を通すことでジッタが低減している様子が

よくわかります。

下:入力信号 上:出力信号

入力に比べて出力の輝線がシャープになっていてジッタが取れている様子がわかります。

ES0918の音質の効果がジッタクリーナにあるなら、これをPCM1704あたりに組み込めば

鬼に金棒かな?

早速組み込んでみましょう!

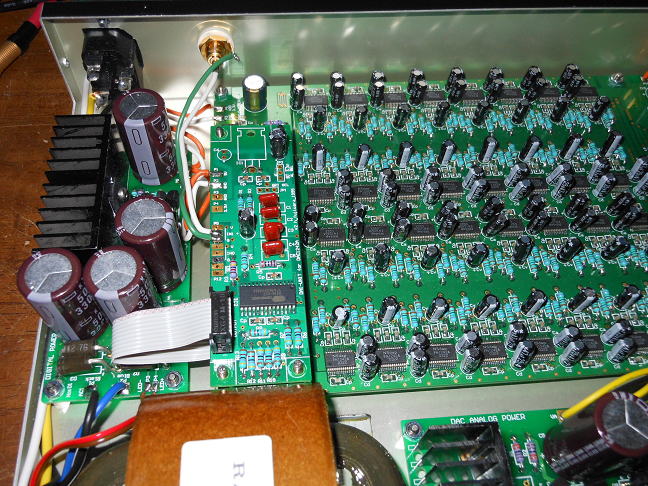

どれに組みこんで見るかDACを物色していたらちょうどスペース的に余裕のありそうなDAC1242-3が眼にとまりました。

私の作例にしては珍しく一層構造なので、薄型のケースで基板上にスペースがあります。試作基板の薄さなら

その隙間に余裕で入ります。

久しぶりにDAC1242-3をご開帳。それにしても32個のFN1242Aが並んでいるのは壮観です。

接続方法は簡単です。DAC基板についている制御信号(FSYSあるいはBCLK)のダンピング抵抗をはずして

その両端をジッタクリーナ基板に接続します。

改造は簡単です。

信号線の配線とジッタクリーナ基板への電源配線をして改造は終了です。

基板が1ポンのビスのみでとまっているので少し強度的に心配ですが、問題なく動くようなら

ちゃんと固定しましょう!

改造後の基板の様子。ちょっと配線が浮いているので、あとで整理しましょう!

動作確認!

まず動作の確認に関しては、どの信号線をジッタクリーナを通すか、そしてどこまでの周波数が

つかえるかの2点になります。

FSYS(システムクロック)をジッタクリーニング

まずはDACのシステムクロックラインに接続して動作確認です。この場合の最高周波数は24.576MHzになります。

これは192kHzを128fsで動作させた場合になります。44.1から192kHzまで問題なく動作しました。

BCK(システムクロック)をジッタクリーニング

つぎはBCKです。こちらの信号の最高周波数は192kHz時で12.288MHzになります。BCKの場合は、入力と

出力の位相がそろっている必要があります。でないと、正確にデータを伝送することができないため、ノイズ

まみれになります。

さて、こちらも問題なく動作しました。

すべてのパターンで動作しました。

いよいよ試聴です!

試聴につかったCDは久しぶりに大黒摩季のアルバムから引っ張ってきました。

まずはFSYSをジッタクリーニングした場合の効果ですが、音の透明度があがったような気がします。

遠くにボールを投げて落ちて地面に当たった音が、ノイズにかき消されずに明瞭に聞こえるような

感じでしょうか。まあ、プラシーボ全開かもです(笑)。

次はBCKをジッタクリーニングした場合です。実際にはこちらが本命と考えています。

というのもFSYSは、DACの内部回路を動かすためのクロックですが、実際の時間軸の基点になるのは

BCKだと思っています。そのためBCKのジッタをいかに減らすかが重要になるはずです。

で、実際に試聴してみると、これもプラシーボ全開かな(爆)。投げたボールが地面に落ちずに、どんどん

伸びていって見えなくなるような音の伸びを感じます。やはりBCKに入れた方が効果があるような気がします。

こんな感じで装置を並べて試聴です。上からASRC、ヘッドホンアンプ、DAC1242-3(ジッタクリーナ付き)。

やっぱり・・・

このまま、DACの中に納めてやろうかとおもいましたが、3.3Vのディジタル電源の放熱板がかなり熱をもっています。

そりゃ、ジッタクリーナーの基板だけで200mA近くの電流を消費します。放熱板は約1W分余計な熱を放熱しないと

いけないので、放熱板の容量からすれば10℃以上は上昇するはずです。

そのまま収納するのはあきらめました。それにジッタクリーナの性能をより発揮させるには電源も分離した方がよいかもです。

それと、DACに接続するには10Pのコネクタ接続ができるようにしたほうが便利かな。

今回の基板は、どちらかといえばSI5317用の変換基板がなくて、動作評価のために試作したようなものですから、

少し使い勝手はよくないです。

どんな基板パターンにしようかな?

V2基板が完成しました。2011.11.8

入出力にDACと接続しやすいように10Pのコネクタを配置したV2基板が完成しました。

Si5317の半田パッドも半田が流れやすいに、穴もすこし拡大しました。

また3.3Vのレギュレータも搭載したので、5V単一電源での動作も可能です。

ジッタクリーナ V2基板が完成しました。

SI5317の裏面パッドに半田が流れやすいように

大きめの穴をあけました。

さっそく組み立ててみましょう。半田付けは細かい作業ですが、特段難しいところはありません。

半田付けのチェックを十分にすればいいのですが、水晶振動子は裏面パッドなので半田が流れているかどうか

わかりにいこともあって、あらかじめ予備半田をしておきました。こうすれば少し浮き上がるので

あとで半田付けができているかどうかが確認しやすくなります。

水晶振動子はあらかじめ予備半田をしました。

完成!

部品点数は少ないので、あっという間に完成です。さて、動作確認は明日にでも行いましょう!

完成したのでお出かけ用の写真をパチリ。

動作確認! 2011.11.14

入力には19.66MHzの水晶発信出力を1/1−1/16に分周できる基板を組んで、簡易信号原としてつかいました。

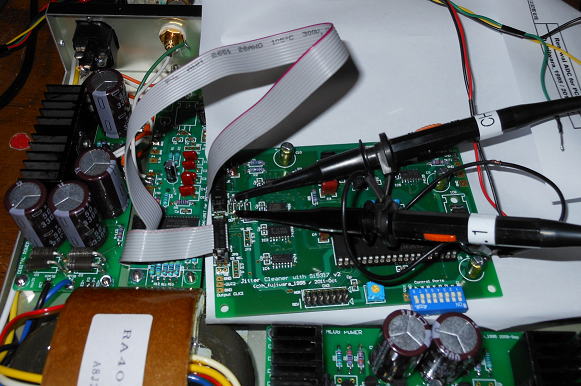

動作確認の様子です。

このジッタクリーナは入力信号に対して出力信号が完全にロックした状態でも、位相差はずれてしまうので、

位相差検知機能をつかって内部で修正します。これはプログラムで行います。

ロックした状態だが位相がずれている。 自動的に位相調整

問題なく動作することが確認できました。このSI5317のジッタクリーナですが、

もっともBW(Band width)を低い周波数に設定すると、ロックするまでに数秒かかることがありますが、

それだけに周波数の安定性は抜群にいい感じです。

実践投入!

動作確認ができたところで、実践投入してみましょう。前回テストしたのはDAC1242-3ですが、

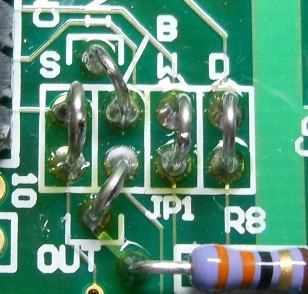

同じDACを使いました。ジッタクリーナをかける場所はB(Bit CLOCK)ですので、この部分を

ジッタクリーナ回路を通過するように基板上のジャンパーを設定します。

通常はD(DATA)とW(WORD CLOCK)はジッタクリーナをかけることは無いので、ここは単なる

ジャンパーです。基板上ではB(BitCLOCK)あるいはS(SystemClock)のどちらかがジッタクリーナ

回路を通るようにジャンパしやすいようにしています。

まずはBitCLOCKをジッタクリーナしてみます。

接続はフラットケーブルだけで行うので簡単です。もう1本、ケーブルを用意して、

DAIとDACユニットの間にジッタクリーナを挟みこみました。

DAC1242-3への組み込み確認の様子!

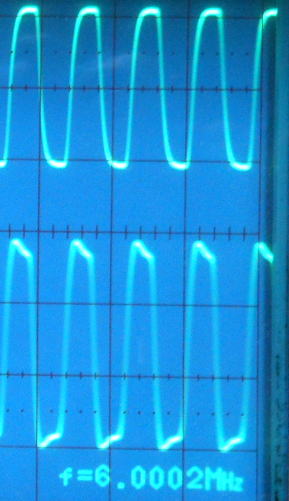

まずは信号を確認して動作しているかどうかのチェックです。BitClock信号を入出力で監視してみましたが、

見事に位相も一致しています。

BitClockの信号の様子(上:入力、下:出力)

安定するまではちょっと我慢

ジッタクリーナでは入力信号(周波数)が変わると、入力に追従して安定するまでに時間がかかります。

もっともBWの値を小さくすると(周波数帯を低くする)、ロックするまでに数秒かかる場合があります。

これは、安定性を示す一つの指標なのですが、安定するまでは信号の位相もずれるので、

アナログ信号にはノイズが生じてしまいます。これについては少しの間の我慢です。

しかし、一度安定してしまえば、あとは非常にクリーンな音が楽しめます。

安定するまではノイズは発生します。 安定すれば、クリーンな音が実現できます。

完成!

さらにDAC1794-5に組み込んでみました。この構成はメモリーバッファーからDAC1794-5に配線されていますが、

途中にジッタクリーナをはさみこみました。あっさり動作できました。

音もいいですね(プラシーボ全開!)・・・・メモリーバッファーの水晶発振回路のジッタがさらに取れたのでしょうか。

それならメモリーバッファー上の水晶発振回路出力をジッタクリーニングしたほうがいいかな?

DAC1794-5での動作確認の様子。

しかし、なんといってもRenew DAC1704との組み合わせが楽しみです!

(つづくかな?)