#### **ClockBuilder Pro Release Notes**

Copyright © Silicon Laboratories Inc. All Rights Reserved.

http://www.silabs.com/cbpro

# Use with the following devices

Si5332, Si5334, Si5335, Si5338, Si5340, Si5341, Si5342, Si5342H, Si5344H, Si5344H, Si5345, Si5346, Si5347, Si5348, Si5350, Si5355, Si5356, Si5357, Si5380, Si5381, Si5382, Si5383, Si5384, Si5386, Si5391, Si5392, Si5394, Si5395, Si5396, Si5397, Si51210, Si51211, Si51214, Si51218

# Use with the following EVBs

Si5332 Si5332-12EX-EVB, Si5332-8EX-EVB, Si5332-6EX-EVB, Si5332-12IX-EVB, Si5332-8IX-EVB, Si5332-6IX-EVB

Si5338 Si5338-EVB

Si534x/7x/8x/9x Si5340-D-EVB, Si5340-EVB, Si5341-D-EVB, Si5341-EVB, Si5342-D-EVB, Si5342-EVB, Si5344-D-EVB, Si5344

Si5344H-EVB, Si5345-D-EVB, Si5345-EVB, Si5346-D-EVB, Si5346-EVB, Si5347-D-EVB, Si5347-EVB, Si5348-D-EVB, Si5348-E-EVB, Si5348-E-EVB, Si5380A-D-EVB, Si5380-D-EVB, Si5381A-E-EVB, Si5381-EVB, Si5382A-E-EVB, Si5391A-A-EVB, Si5391P-A-EVB, Si5392E-A-EVB, Si5394A-A-EVB, Si5394E-A-EVB, Si5394P-A-EVB, Si5394B-A-EVB, Si538B-A-EVB, Si538B

EVB, Si5395A-A-EVB, Si5395E-A-EVB, Si5395P-A-EVB, Si5397A-A-EVB

Si535x Si535X-B20QFN-EVB, Si5356-EVB, Si5357-EVB

Si51211x Si51211-EVB, Si51218-EVB

Note: Si5338/50/51 EVB not supported on Windows XP

# **PC System Requirements**

Operating System:

ClockBuilder Pro (CBPro) requires Windows XP Service Pack 2, Windows Vista Service Pack 2, Windows 7 Service Pack 1, Windows 8, or Windows 10. Either 32- and 64-bit versions are supported.

CBPro uses Microsoft.NET Framework version 4.0. The installer will check to see if it is installed and, if not, prompt to automatically download and install it. Windows 7 and higher PCs will normally already have .NET 4.0 installed.

If you need to install CBPro on a PC that does not have an Internet connection and does not have .NET 4.0, you can download Microsoft's stand-alone installer from <a href="http://www.microsoft.com/en-us/download/details.aspx?id=17718">http://www.microsoft.com/en-us/download/details.aspx?id=17718</a>. Install I.NET 4.0 before running the CBPro installer.

1024 x 768 screen resolution or greater

USB 2.0 or higher if you want to connect to a supported EVB

# **Revision History**

| Version 2.31 [2019-03-25]       | 4  |

|---------------------------------|----|

| Version 2.30.1 [2019-02-19]     | 4  |

| Version 2.30 [2019-02-19]       | 4  |

| Version 2.29 [2018-11-4]        | 5  |

| Version 2.28.1 [2018-09-24]     | 5  |

| Version 2.28 [2018-09-24]       | 5  |

| Version 2.27 [2018-08-10]       | 8  |

| Version 2.26.0.1 [2018-06-28]   | 9  |

| Version 2.26 [ 2018-06-24 ]     | 9  |

| Version 2.25 [ 2018-06-04 ]     | 9  |

| Version 2.24 [ 2018-05-23 ]     | 10 |

| Version 2.23 [ 2018-04-10 ]     | 11 |

| Version 2.22.1 [ 2018-03-28 ]   | 11 |

| Version 2.22 [ 2018-03-27 ]     | 11 |

| Version 2.21 [ 2018-01-19 ]     | 14 |

| Version 2.20 [ 2017-11-21 ]     | 15 |

| Version 2.19.3 [ 2017-09-25 ]   | 17 |

| Version 2.19.2 [ 2017-09-25 ]   | 17 |

| Version 2.19 [ 2017-09-24 ]     | 17 |

| Version 2.18 [ 2017-09-17 ]     | 18 |

| Version 2.17 [ 2017-09-11 ]     | 18 |

| Version 2.16.1 [ 2017-07-19 ]   | 19 |

| Version 2.16 [ 2017-07-18 ]     | 19 |

| Version 2.15 [ 2017-05-12 ]     | 21 |

| Version 2.14 [ 2017-04-21 ]     | 21 |

| Version 2.13.0.1 [ 2017-03-27 ] | 24 |

| Version 2.13 [ 2017-03-03 ]     | 24 |

| Version 2.12.1 [ 2016-12-15 ]   | 25 |

| Version 2.12 [ 2016-12-12 ]     | 26 |

| Version 2.11.1 [ 2016-10-26 ]   | 27 |

| Version 2.11 [ 2016-10-24 ]     | 27 |

| Version 2.10 [ 2016-09-07 ]     | 29 |

| Version 2.9 [ 2016-7-29 ]       | 30 |

| Version 2.8 [ 2016-4-24 ]       |    |

| Version 2.7.1 [ 2016-4-20 ]     |    |

| Version 2.6 [ 2016-3-29 ]       |    |

|                                 |    |

| Version 2.5 [ 2016-2-23 ]    | 32 |

|------------------------------|----|

| Version 2.4.0.3 [ 2016-1-8 ] | 33 |

| Version 2.4 [ 2015-12-8 ]    | 33 |

| Version 2.3.1 [ 2015-11-4 ]  | 34 |

| Version 2.3 [ 2015-10-26 ]   | 34 |

| Version 2.2 [ 2015-09-10 ]   | 37 |

| Version 2.1 [ 2015-08-18 ]   | 38 |

| Version 2.0.2 [ 2015-06-16 ] | 40 |

| Version 2.0 [ 2015-06-15 ]   | 40 |

| Version 1.8 [ 2015-04-30 ]   | 41 |

| Version 1.7.1 [ 2015-04-03 ] | 41 |

| Version 1.7 [ 2015-03-26 ]   | 42 |

| Version 1.6.1 [ 2015-02-12 ] | 44 |

| Version 1.6 [ 2015-02-11 ]   |    |

| Version 1.5 [ 2014-12-03 ]   | 46 |

| Version 1.4 [ 2014-11-5 ]    | 47 |

| Version 1.3 [ 2014-11-2 ]    | 47 |

| Version 1.2 [ 2014-09-09 ]   | 52 |

| Version 1.1 [ 2014-08-13 ]   | 53 |

| Version 1.0 [ 2014-07-30 ]   | 55 |

# Version 2.31 [2019-03-25]

# Si534x/8x/9x:

- Si5395: modified project conversion from Si5345 to Si5395: map OUT9 to OUT9A (TMGSW-1039)

- Si5380/86/91/95: the output diagram was updated to show R dividers (TMGSW-992)

- Si5342H/44H DCO changes (TMGSW-1045)

- o Removed the DCO mode selection: only direct register mode is supported (no FINC/FDEC)

- o The design report now always shows the direct register write equation

- o MXAXB\_FSTEP\_MSK and MXAXB\_FSTEPW are excluded from the design report, exports, etc.

# Si5391/2/4/5P: (TMGSW-1035)

- Input/output frequency ranges have been updated

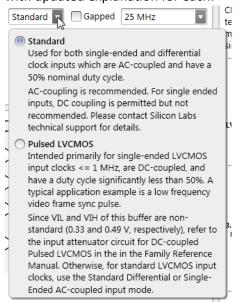

- Input format: only "Standard" mode is supported on IN2/IN3 (no LVCMOS, no Pulsed CMOS, no single ended of any type)

- Output format: custom differential has been removed; HCSL is restricted to 25/50/100/125/200 MHz

- The fixed N divider assignments have been updated

- The EVB sample projects have been updated

- An output's P-Grade status/capability is reported via a new widget on the output page; the coupling check is still

performed, but is only shown if there is a coupling issue not covered by one of the P-Grade rule checks for

domain 1 (156.26/312.5/625 MHz) frequencies

Updates for pre-release devices.

# Version 2.30.1 [2019-02-19]

Si534x/8x/9x: fixed: clicking a checkbox on the INTRb mask page had no effect

# Version 2.30 [2019-02-19]

#### Si534x/8x/9x:

- Fixed: Si5340/41/42/44/45/81/82/86/91/92/94/95: the frequency planner could not always find a solution when an output had a high resolution fractional component; example, 322\*419020819/418995225 MHz (TMGSW-988)

- Fixed: if DCO was enabled on a PLL and then it is changed to free run only mode, you would receive an error when trying to calculate the frequency plan

- Si5392P/94P: improved phase noise performance (TMGSW-827)

- Si5391/2/4/5P: disabled export for in-system programming; please contact Silicon Labs for assistance

- Si5380/81/82/86, Si5391/2/4/5P: increase preamble delay from 300 ms to 625 ms to account for worst case device calibration time

- Si5340/1 Rev B,D: I/O Skew support removed

- Si5346/47/96/97 All PLLs, Si5348/83/81/82/88 DSPLL A/C/D: when possible, select fractional P divider to keep Fpfd >= 100 kHz, resulting in less output jitter in some cases (TMGSW-1019)

- Si5349/80/81/82/86: changed the minimum loop bandwidth to 20 Hz on DSPLLB when XO selected (TMGSW-1017)

### Si5335:

- Fixed: datasheet addendum did not show assigned output voltage (TMGSW-981)

- Fixed: CBPro and datasheet contradicted RESET function pin assignment (TMGSW-1033)

Updates for pre-release devices.

# Version 2.29 [2018-11-4]

### Si534x/7x/8x/9x:

- Fixed: the I2C address burn tool gave "Object reference not set to an instance of an object" error

- Update CBProFOTF1 CLI to support frequency-on-the-fly (FOTF) on multi-PLL devices when PLL is in "free run only" mode

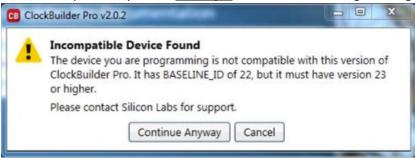

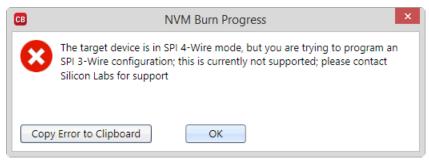

- Using field programmer and socket, support burning NVM when target device and project file SPI mode do not

match. I.e. target is configured for 4-wire and project is 3-wire (and vice versa). The support is automatic: there

is nothing for user to do.

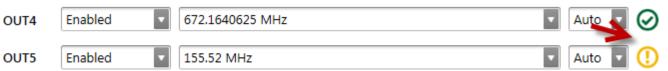

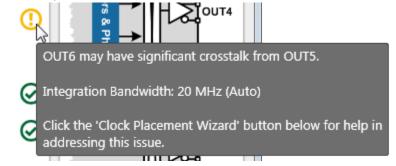

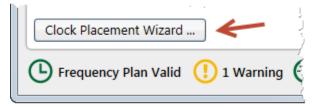

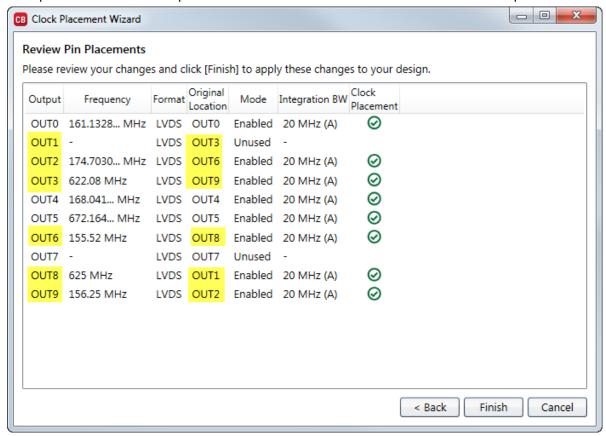

- Coupling (crosstalk) DRC footnote explains harmonic contribution to the coupling check

#### Si5332:

- Fixed: a device that had NVM burned using the field programmer with CBPro 2.27.2 through 2.28.4 would not

operate normally when coming out of reset; any parts programmed with this version can be recovered by

burning the desired configuration a second time with CBPro 2.28.5 or higher

- Fixed: writing Si5357 project file via field programmer over-wire was causing a part mismatch error

### Si5334/38:

Fixed: EVB DUT write was failing PLL calibration when input source was IN4 or IN5/6

Updates for pre-release devices.

# Version 2.28.1 [2018-09-24]

Support Si5348 Rev E (Network Synchronizer for SyncE/ 1588 PTP Telecom Boundary (T-BC) and Slave (T-SC) Clocks)

# Version 2.28 [2018-09-24]

#### Si5332:

- Fixed: MultiSynth dividers were keeping spread spectrum settings even though outputs were set to "Auto" divider

- Fixed: GPIOs were configured backwards for Multiprofile, for example, LSB was being set as MSB

- Fixed: Multi-profile NVM required size calculation was missing 2 bytes per frame

- Fixed: Setting output as buffer was displaying corresponding R divider as being unused

- Fixed: multi-profile GPIO configuration was adding extra bytes for unused pins when translated to NVM

- Fixed: output buffer was triggering DRC error when bank was previously set to divider

- Fixed: C code header export had 16-bit addressing instead of 8-bit

- Add one time Field Programmer support for multi-profile projects

### Si5335/55:

- Fixed: FS pin assignments in the GUI were swapped for 3 profile configuration. P1 was FSO and it should be FS1 and P2 was FS1 and should be FSO. This was not causing a functional issue but it was not in agreement with the datasheet. Pin frequency select behavior is now driven by number of profiles

- Fixed: DUT Write read back was failing because of REVID setting is read-only, when writing to EVB this setting is now ignored

- Fixed: DUT Write was hanging when trying to perform the VCO calibration step if no signal is provided, the DUT write now fails gracefully after 500ms

- Enabled the ability for users to specify loop bandwidth at a profile level, rather than being global

# Si534x/7x/8x/9x:

- Si5380: Fixed: DRC warning "When in Zero Delay Mode, because N0 is within the feedback loop, any

phase/delay adjustments to the output clocks coming from N0 will have no effect" was shown even when ZDM

was not enabled

- Support static I/O skew adjust on Si5381/2/6 Rev E

- Improve Si5341/45 -> Si5391/95 Project Conversion:

- Fixed: if OUT0 or OUT9 in the original 41/45 projects had manual N divider assignments and OUT0A or OUT9A were later enabled in the 91/95 project, there was a frequency planner error; future converted projects will not have this issue; if any previously imported project has this issue, you can fix the new project by temporarily changing the divider assignment to Auto and then back to the specific divider

- OUT0A and OUT9A disabled state is now set to the existing OUT0 and OUT9 value

- OUTOA and OUT9A output frequencies are set to OUT0 and OUT9 respectively (but still set to Unused)

- No longer distinguish between harmonic and significant crosstalk in output page [!] icon color and tooltip: always show solid yellow and use phrase "may have coupling" in the tooltip

- Frequency-on-the-Fly (FOTF):

- o Added support for FOTF on Si5348/83/84 with the following restrictions:

- DSPLL B inputs, outputs, bandwidth, etc. cannot be adjusted

- On Si5383/84/89, if a 1 Hz (1pps) input is present, DSPLL D cannot be adjusted

- A 1 Hz output frequency cannot be set in a plan file; it can only be present in the base project (but can be switched to non-1 Hz in a plan)

All of the restrictions above are enforced by the tool

- Further restrict multi-PLL such that FOTF is not supported on a PLL that has an input that is shared with another PLL

- Update user manual and in-system programming overview to reflect this

- Move output disabled state and format to existing output frequency pages for all parts

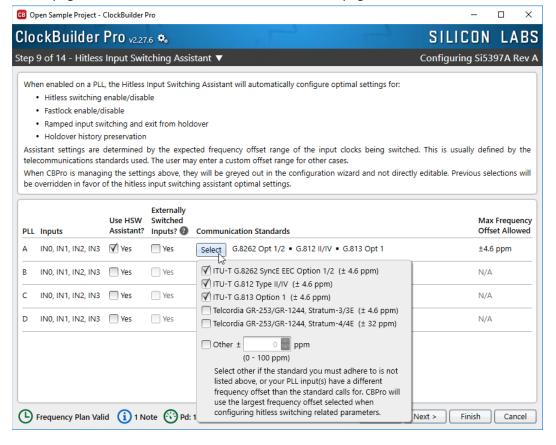

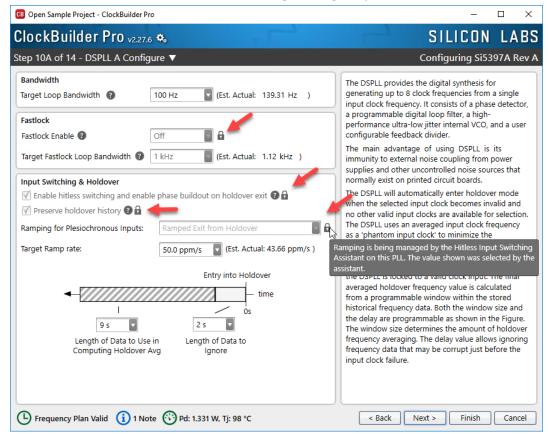

New Si5381/2/6, Si5392/4/5/6/7, Si5348 Rev E Hitless Input Switching Assistant:

• A new page is available in the wizard, before the DSPLL page:

When assistant is enabled on a PLL, the settings managed by it are auto set and locked:

Bandwidth recommendations are made via DRC notes:

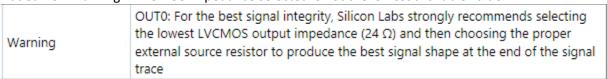

| Ignore? | Category 🔺 | Message                                                                                                                        | Note |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------|------|

|         | Note       | DSPLL A: selecting the highest bandwidth allowed by the application is recommended to minimize phase deviation on input switch | [1]  |

|         | Note       | DSPLL C: selecting the lowest bandwidth allowed by the application is recommended to minimize phase deviation on input switch  | [1]  |

#### Footnotes:

- Recommendation is based on the frequency plan and selections in the hitless input switching assistant. Loop bandwidth is configured on the "DSPLL Configure" page of the CBPro wizard.

- A new section is included in your design report:

# Version 2.27 [2018-08-10]

#### Si5332:

- Support Revision D

- Support encapsulated crystal packages (grade E/F/G/H)

- Support Si5332-12IX-EVB, Si5332-8IX-EVB, and Si5332-6IX-EVB encapsulated crystal EVBs

- Support multi-profile mode

- Up to 32 profiles can be configured via up to 5 profile select pins

- Selectable global or per-profile feature configuration to speed data entry and ensure synchronization of configuration common between profiles

#### Si534x/8x/9x:

- Fixed: CBProProjectSettingsExport was not including SiLab bank registers that are included in the CBPro GUI register/settings export

- Fixed: could receive export/write/OPN error regarding LOLx\_INT\_TIMER\_SCL if fastlock bandwidth was low (or fastlock was disabled and loop bandwidth was low)

- Si5348/83/84: Fixed: on input clock selection mask, IN3/IN4 checkboxes were enabled even though they have no effect and OOF is not supported

- Si5348/83/84: new DRC error if hitless switching is enabled on PLL with IN3/4 CMOS input

- For all parts that allow mix of integer N < 10 and fractional N > 10, in certain cases the frequency planner could

not find a solution when there was a mix of frequencies > Fvco(min)/20 and those that require N < 10</li>

- Show OOF[3] disabled when ZDM is enabled

- Set OOF\_EN[3] and FAST\_OOF\_EN[3] to 0 and clear THR/etc settings for ZDB

- Disable INTR mask checkbox and clear OOF INTR MSK[3]

- Don't allow DCO on N0 if ZDM is enabled: add DRC error if already configured in project; customize lock icon in DCO editor

- Add DRC warning if set non-zero I/O delay on N0 if ZDM is enabled

# Version 2.26.0.1 [2018-06-28]

# Si5332/57:

• Fixed: NVM burn with field programmer socket or wired would result in invalid NVM configuration. This bug was introduced in CBPro 2.25.2

# Version 2.26 [ 2018-06-24 ]

Added Support for Si5391 (Low-Jitter, 12-Output, Any-Frequency, Any-Output Clock Generator)

- Detects and controls a SI5391A-A-EB and SI5391P-A-EB

- Can create a custom factory programmed part (Orderable Part Number)

- Can export a configuration for in-system programming using I2C or SPI

- Supports NVM burning through field programmer socket and wired to customer PCB using serial cable

#### Si534x/8x/9x:

- Fixed: if DSPLL C or D were used in a configuration, pin control mode on DSPLL B was ignored and register controlled mode was configured via IN SEL REGCTRL PLLB

- Fixed: some older CBPro project files could not be opened on German (and possibly other) PCs; would get the equivalent of "bad data" as the error message

- Fixed: Si5340/1: if only a single input was defined and ZDM was enabled, received DRC error "must define a non-Zero Delay Mode input on DSPLL" erroneously

- Si5392/4/5/6/7: update documentation links

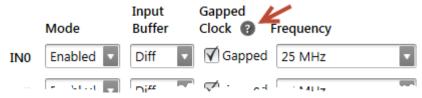

- Si5349/80/86: changes for Fpfd >= 1.024 MHz: minimum DSPLL B loop bandwidth in ZDM relaxed from 100 Hz down to 10 Hz; minimum gapped input clock frequency requirements increased by a factor of two

- Small updates to fractional P divider / gapped clock and input frequency warning thresholds based on PFD frequency and selected loop bandwidth

# Si5334/35/38/55/56/57:

- Fixed: LVCMOS In-Phase format was raising an error when trying to submit an OPN

- Fixed: Si5338 NVM file conversion to CBPro project now works even if the resulting CBPro project has a

frequency planner error, possibly due to ClockBuilder Desktop allowing synthesis errors. CBPro will show the

DRC error(s) after opening the converted file.

#### Si5332:

- Fixed: Field programmer communication config dialog was not properly setting communication to I2C, it was remembering previously set mode

- Fixed: LVDS Fast power calculation was showing 0 W in design report

# Version 2.25 [ 2018-06-04 ]

Added Support for Si5392/4/5 (Up to 12 Output Any-Frequency, Any-Output Jitter Attenuator/Clock Multiplier with Ultra-Low Jitter)

Added Support for Si5396/7 (Dual/Quad DSPLL™ Any-Frequency, Any-Output Jitter Attenuator)

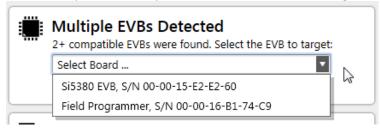

• Detects and controls a SI5394A-A-EB, SI5394P-A-EB, SI5395A-A-EB, SI5395P-A-EB, and SI5397A-A-EB Evaluation Boards

- Can create a custom factory programmed part (Orderable Part Number)

- Can export a configuration for in-system programming using I2C or SPI

- Supports NVM burning through field programmer socket and wired to customer PCB using serial cable

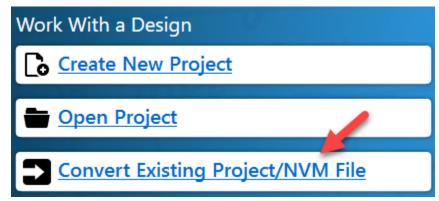

- Existing Si534x project files can be converted to equivalent Si539x design using the new project conversion tool, available from the CBPro welcome screen:

See AN1155 Differences between Si5342-47 and Si5392-97 for more information

#### Misc:

• Fixed: closing a popup using the down arrow can cause opening another popup not to work, instead showing the previous popup

# Version 2.24 [ 2018-05-23 ]

Added Support for Si5357 (12-Output Any-Frequency Clock Generator)

- Detects and controls a Si5357 Evaluation Board (Si5357-EVB)

- Can create a custom factory programmed part (Orderable Part Number)

- Can export a Si5357 configuration for in-system programming using I2C

- Support NVM burning through field programmer socket and wired to customer PCB using serial cable

#### Si5334/35/38/55/56:

- Fixed: Si5338 datasheet addendum was missing output format voltage and pin 6 description was incorrect

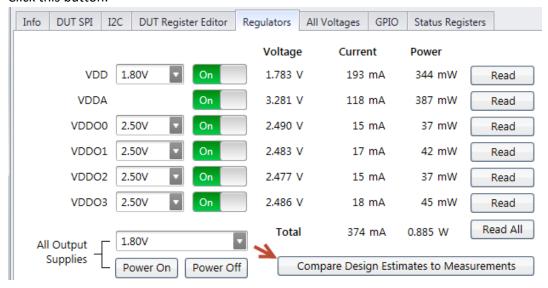

- Fixed: EVB regulators were not in sync with output format voltage

# Si5332:

- Fixed: the frequency planner could select a PFD frequency (Fpfd) outside of the maximum limit. This could only occur for configurations with input frequencies greater than 50 MHz.

- Fixed: Field Programmer could not talk to devices configured at 1.8/2.5V IO voltage

- Fixed: PLL was not being disabled for Buffered only parts

- Fixed: Register export was missing registers to switch the part between ready and active mode

- Changed default output driver format to LVPECL

- Added support for Single LVCMOS output driver format

- Added support to select from internal/external termination for HCSL driver format

# Si534x/8x:

- Fixed: FOTF for Si5340/41/42/42H/44/44H/45 could give error "some outputs on the same VDD supply do not have an even common multiple within the Fdco range" when there is no issue

- Fixed: bandwidth could be set lower than needed

- Fixed: planner could give error "calculated NF, Infinity, is too large for register"

- Si5380: support phase noise estimate tool

- Make CBProFOTF1.exe the documented, primary name for Si534x/8x FOTF; allow CBProSi534x8xFOTF.exe to be run still for backwards compatibility

#### Misc:

- Fixed: the field programmer selector in Design Dashboard was not customized for non-Si534x/8x families when the socket was missing

- Show special message in Orderable Part Number / Phase Noise Request wizard if user has not consented to the new silabs.com data policy

- Updates to CBPro Tools & Support for In-System Programming

- Improved support for pre-production devices

# Version 2.23 [ 2018-04-10 ]

Added support for Si5334/35/38/55A/56A, Si5338-EVB, and Si5356-EVB.

# Si534x/8x:

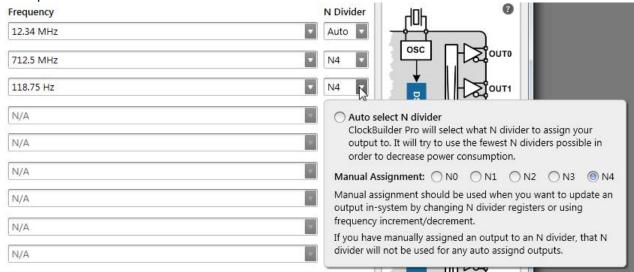

- Fixed: high frequency outputs (require Nx<10) could not always be manually assigned to an Nx divider

- Add tooltip to explain DCO Range

# Si5381/2/6 Phase Noise Estimate Tool:

- Fixed: closing CBPro without first closing the PN window would leave hung CBPro running in the background

- Do not calculate estimate if the output frequency is less than 10 MHz

- Set the maximum frequency of the input phase noise plot to be no higher than the maximum frequency of the output phase noise plot

- Update output selector items if an output is added/removed from project while the tool window is still open

- Misc. user interface

# Version 2.22.1 [ 2018-03-28 ]

#### Si534x/8x:

Fixed: NVM program tool could abort with "error parsing NVM file"

# Version 2.22 [ 2018-03-27 ]

#### Misc:

• There is a new EVB/USB driver README in C:\Program Files (x86)\Silicon Laboratories\ClockBuilder Pro\Drivers. Please review it if CBPro is not detecting a supported Silicon Labs Timing EVB.

# Si5332:

Register exports created by CBPro GUI Export tool, CBProProjectRegistersExport CLI, and related CLIs now

include preamble and postamble required to fully reconfigure the device (via register 0x06 write).

#### Si534x/8x:

- Si5342H/44H: support outputs down to 100 Hz (was 8 kHz)

- Si5340/1/2/4/5: jitter optimization has been improved when DCO is enabled on a MultiSynth. When DCO is enabled, the planner priority page is no longer shown. A MultiSynth (Nx) divider that was previously integer may now have a fractional value after this change, to reduce jitter across all outputs (DCO and non-DCO).

- Si5346/47/96/97: better error message if can't calculate a frequency plan due to required resolution of dividers

- Si5380: default OLPD gain now varies depending on reference type: XTAL=1,XO=8; previously it was always 1. When using a low noise XO, increasing the OLPD gain improves the close in phase noise. This change is consistent with the default settings for the rest of the Si538x devices.

- Si5380: switch to XO as default reference for rev D

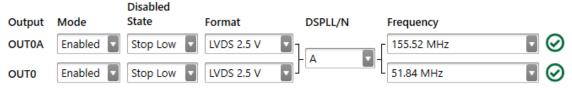

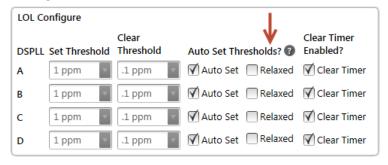

- Si5380/1/2/6: the clock output editor and frequency planner now supports discrete frequency entry and driver configuration on OUTO/OA and OUT9/9A. For example:

- If an Si5381/2 CEVB rev D is detected, "Open Default Plan" will set XAXB mode to XTAL

- Change Si5344 EVB sample input select mode to auto-revert

### New Si5381/2/6 Phase Noise Estimate Tool:

- Supports three input phase noise data modes:

- Jitter generation only (-200 dBC/Hz input)

- Very high input jitter example

- o Custom PN CSV file

- Calculates RMS Jitter calculation, with configurable integration bandwidth

- Can save PDF report

- Can save plot data to CSV

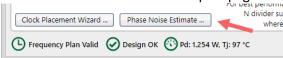

- Launched from CBPro wizard Outputs page:

# Improved Si5346/47 FOTF (CBProSi534x8xFOTF CLI):

- Updated preamble and postamble in DSPLL plan scripts to ensure PLL operates as expected on plan change. In prior releases, a PLL could generate wrong frequency(s) after PLL plan script write.

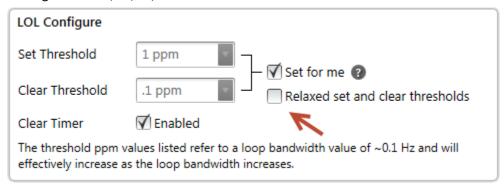

- LOL and OOF settings can now be configured in plan scripts:

- LOL thresholds for a DSPLL can optionally be changed using the LOL\_SET\_THR and LOL\_CLR\_THR keywords. Decimal values are accepted. Can only be used if the base project file has "Auto Set" unchecked.

- OOF thresholds for an input can be set using the OOF\_SET\_THRx, OOF\_CLR\_THRx (precision OOF) and FAST\_OOF\_SET\_THRx, FAST\_OOF\_CLR\_THRx (fast OOF) keywords, where x is the INx input number starying at 0. Thresholds can only be specified if the Enabled checkbox is set on the corresponding input. Decimal values are supported for precision OOF and integer values for fast OOF. OOF can only be changed on an input that feeds a single DSPLL.

- o Example:

```

1,LOL_SET_THR,30

1,LOL_CLR_THR,3

1,OOF_SET_THR0,10

1,OOF_CLR_THR0,1

1,FAST_OOF_SET_THR0,2000

1,FAST_OOF_CLR_THR0,1000

```

- Si5346/7 plan scripts now contain read-modify-write mask column. When mask is not 0xFF, read-modify-write should be performed for the register write.

- Under certain FOTF conditions, PLL settings that share a common address/register may need to change on a per-plan basis

- For example, LOL\_SLW\_DETWIN\_SEL\_PLLA and LOL\_SLW\_DETWIN\_SEL\_PLLB share the same register, 0x009B

- o PLL DCO frequency or target bandwidth change can affect these values

- Writes to registers that have multiple PLL settings (bitfields) at the address therefore now have a readmodify-write mask

- The mask is documented within the PLL plan script via comment:

- Address, Value, Mask

- # If mask is 0xFF, no read-modify-write is required. Otherwise,

- # read register value and write to device Read&~Mask + Value&Mask

- o Example:

- # Write Configuration

- 0x009B,0x56,0xF0

- 0x009D,0x95,0x0C

- 0x00A9,0x35,0xFF

- 0x00AA,0x0A,0xFF

- o The first two writes require read-modify-write. The last two do not.

- Only Si5346/7 FOTF plan scripts will contain the mask. The full config script does not. Other parts, like single PLL Si5345, do not include the mask at all.

- DSPLLx-Register-Script-All-Plans.csv files are no longer created by the tool because of more complex preamble/postamble. If any file is found in the output folder, it is removed to ensure existing users of tool do not try to use the out-of-date script.

- Device revision B is no longer supported by the FOTF tool. The updated preamble and postamble required to guarantee configured output frequency on PLL plan change is not supported by Si5346/7 revision B. If you try to run the CBProSi534x8xFOTF CLI against a revision B project file, the tool will abort with an error.

- The samples, CLI manual, and programming overview deck have been updated for recent changes (mask,LOL,OOF)

Read-Modify-Write Mask is Supported by Register Write Tools:

- The EVB GUI File->Write Register File to Device feature now supports optional read-modify-write mask, allowing new Si5346/7 FOTF scripts to be tested

- Mask is after data; e.g.

- Address, Data[, Mask]

- Spaces and tabs can also be used to separate fields

- CBProDeviceWrite CLI --registers mode also can handle the mask field

- Example for Si538x/4x:

- o mask1.txt:

- 0x026B 0xFF 0x0F <- Only write lower nibble of register; upper nibble is kept as is and data in second column is ignored when masked

- CBProDeviceWrite --registers mask1.txt

Searching for EVBs/FPs ...

# New CBProRegistersToSettings CLI:

- Breaks out device register values by named setting (bitfield).

- For example, if the device is Si5345 Revision D and regs.txt contains:

```

0x0302,0x00

0x0303,0x00

0x0304,0x00

0x0305,0x80

0x0306,0x05

0x0307,0x00

0x0308,0x00

```

0x0309,0x00

0x030A,0x00 0x030B,0x80

CBProRegistersToSettings --part si5345 --rev d --infile regs.txt:

Text, CSV, and HTML output format is supported using the --format option

# Version 2.21 [ 2018-01-19 ]

#### Misc:

Fixed: EVB detection could fail on Windows XP

#### Si534x/8x:

- Fixed: when exporting or writing a free run only project, could get error "input clock select mode must be defined"

- Fixed: Si5349/81/82: in ZDB mode, Fpfd(min) of 1 MHz was not being enforced

- All bandwidths forced to be Fpfd/40 or less; previously fastlock could be up to Fpfd/20

- Based on Px divider, Fpfd, & ZDM state, apply bandwidth range restrictions on fastlock and holdover exit bandwidth the same as loop bandwidth

- Include device grade in EVB labels in all cases:

• For select configurations, the wizard header now reflects possible OPN grades based on Fout(max) and possibly fractional MultiSynth state:

Configuring Si5345ABCD Rev D

# Configuring Si5345AC Rev D

#### Si5332:

- Fixed: Changing XAXB input mode was not updating its use to PLL and causing a DRC error

- Fixed: register and setting exports were displaying 2 byte address instead of 1 byte address

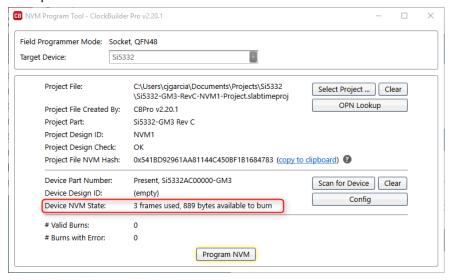

### New Si5332 NVM Program Tool:

- Device to program can be:

- In field programmer socket (Si5332-32SKT-DK, Si5332-40SKT-DK, Si5332-48SKT-DK)

- Wired to customer PCB using serial cable

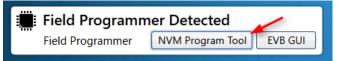

- Launched from CBPro Welcome page, just like when targeting Si538x/4x

- Scan reports on the number of non-volatile memory frames used, available free memory, and the part's OPN

- Note: if the Field Programmer's firmware needs to be upgraded to support Si5332, a dialog will prompt the user to

upgrade the firmware upon programming a DUT's NVM. If upgrade fails, there is a new tool in CBPro's Start menu

Misc folder to re-flash a Field Programmer with corrupt firmware. This would only occur if user disconnects field

programmer during the one time firmware upgrade process.

- Example:

# Version 2.20 [ 2017-11-21 ]

### Misc:

- Fixed: rare crash when trying to select save filename in export, etc.

- Fixed: CBProMultiProjectExport.exe CLI was not creating delta full reconfigure scripts even though it was documented to do so

- The USB driver now fully supports Windows 10 UEFI Secure Boot PCs via a certified driver that is installed on such PCs. Non-secure boot PCs will continue to use the existing driver.

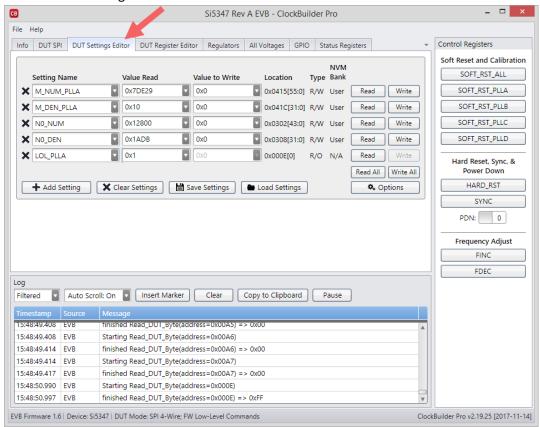

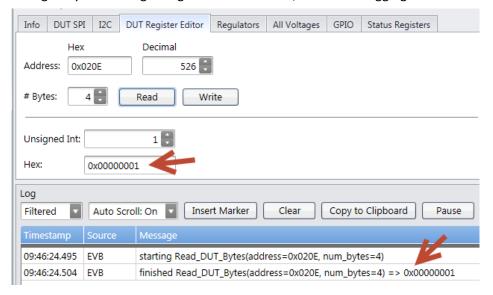

New Settings Editor in EVB GUI:

- Read and write registers based on their setting names (aka bitfields)

- Supported on Si5332, Si535x, and Si538x/4x: EVB or field programmer

- New tab next to Register Editor

- CBPro automatically saves your current settings group to its preferences, keyed off of part number. So when you relaunch, they will be reloaded. But you can also save a group to a text file using the "Save Settings" button, and later restored using the "Load Settings" button

- Example saved settings file:

- # Si5347 Settings

- # Saved by ClockBuilder Pro v2.19.25 [2017-11-14] EVB GUI Settings Editor

- # Saved on 2017-11-14 15:53:05 GMT-06:00

- SettingName, Location, Type, NVM, ReadValue, WriteValue

- M\_NUM\_PLLA,0x0415[55:0],R/W,User,0x7DE29,0x0

- M\_DEN\_PLLA,0x041C[31:0],R/W,User,0x10,0x0

- NO NUM, 0x0302[43:0], R/W, User, 0x12800, 0x0

- NO DEN,0x0308[31:0],R/W,User,0x1ADB,0x0

- LOL\_PLLA,0x000E[0],R/O,None,0x1,0x0

### Si5332:

- Fixed: adding spread spectrum pin could cause error, preventing the plan from being calculated

- Fixed: Spread Spectrum not working in grades C and D Orderable Part Numbers (OPNs)

- Modified Output Enable (OE) universal hardware pin to be OE bar

- Added support for Si5331 CEVB

#### Si51218:

Fixed: mux was configured incorrectly for two clock outputs

# Si538x/4x:

- Fixed: in rare cases, enabling outputs on old project files could crash CBPro

- Fixed: if DCO step size was the same as range, design report would list output as "DCO not supported on this output"; device settings were still OK

- Fixed: exporting firmware boot record or upgrading firmware on Si5383/4 was not working on 32-bit Windows

- Fixed: clicking the input priority arrow very fast could crash CBPro

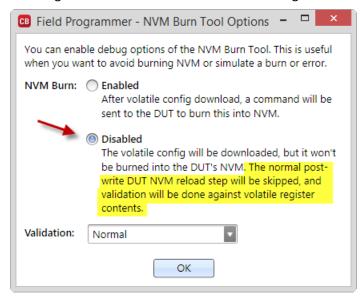

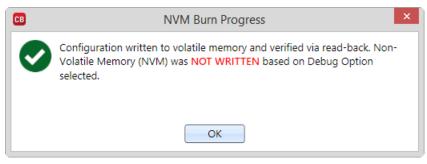

- The NVM Program Tool now validates volatile writes before initiating burn; if mismatch, burn is aborted and user is notified of differing registers

- Si5381/2/6: Grade A (external) reference frequency now selected via pulldown, limited to 48.0231 MHz and 54MHz

- Si5348/83/84: the setting (register bitfield) name for REF priority was changed from IN3\_PRIORITY\_PLLx to REF\_PRIORITY\_PLLx

- Si5346/47/48/83/84: the following settings were removed from exports, design reports because they do not apply to these devices:

- o 0x0240[1] MXAXB FSTEP DEN

- o 0x0240[0] MXAXB\_FSTEP\_MSK

- 0x0241[43:0] MXAXB FSTEPW

- The frequency planner for Si5340/1/2/4/5 and Si5381/2/6 has been improved to allow integer N<10 across a wider range of output frequencies. Previously this set out outputs:

- o 20 MHz

- o 40 MHz

- o 60 MHz

- o 140 MHz

would not be placed on single N divider. Now they are, via automatic or manual N divider assignment

Updates for pre-release devices.

Version 2.19.3 [ 2017-09-25 ]

#### Si5382:

• Fixed: CBPro could crash on free-run only wizard page

Version 2.19.2 [ 2017-09-25 ]

#### Si5332:

Fixed: DRC error was taking into account unused clock outputs in VDDO check

# Version 2.19 [ 2017-09-24 ]

Added support for Si5381/82 12-channel Multi-DSPLL Wireless Jitter Attenuating Clocks

Added support for Si5386 12-channel, Any Frequency, Wireless Jitter Attenuating Clock

#### Misc:

• Fixed: when a project file was opened by double clicking it from Explorer, Outlook, etc. the filename was not reused when you later re-saved, created a design report, etc.

Si538x/4x:

- Remove 0x0402 and 0x0502 addresses from exports on select parts, where the register values never vary from factory programmed values, are never modified by CBPro, and would never be reprogrammed by customers.

- Small modification to BW0-BW5 DSPLL coefficient calculation. Generally will not result in operational bandwidth

change on device, just +-1 change in any one BW0-BW5 setting value. I.e. the "actual bandwidth" value reported

in the CBPro design report will normally not change as a result of this update.

#### Si5332:

- Fixed: changing output format to LVCMOS was not updating properly the output frequency range

- Fixed: Output skew page was incorrectly displaying "ns" instead of "ps" for the offset

- Fixed: frequency planner could select N divider outside range in certain cases, resulting in visible Design Rule

Check error

- Added part grade description to OPN Wizard

# Version 2.18 [ 2017-09-17 ]

Si5332 Support Added (6/8/12-Output Any-Frequency Clock Generator):

- Detects and controls a Si5332 Evaluation Boards (Si5332-12EX-EVB, Si5332-8EX-EVB, Si5332-6EX-EVB).

- Can create a custom factory programmed part (Orderable Part Number)

- Can export a Si5332 configuration for in-system programming using I2C

Updates for pre-release devices.

# Version 2.17 [ 2017-09-11 ]

#### Misc:

Add new --noscan-in-fp-registers-mode option to CBProDeviceRead and CBProDeviceWrite CLIs. Communication

with the device using the field programmer is normally verified before an operation by reading fixed

identification register(s) such as PN\_BASE on Si538x/4x. Specifying this option will disable this behavior when -registers mode is used.

### Si538x/4x:

- Fixed: Si5342H/44H: in register export scripts, don't include 0x0540=0x00 register write (OLB\_TM\_OUT\_ZERO=0) in postamble if DCO mode is enabled. This needs to remain 0x01 (OLB\_TM\_OUT\_ZERO=1) to disengage the other loop. This bug was introduced in CBPro 2.13.3.

- Fixed: when targeting device using field programmer, writing a rev B project file would yield an error due to locked SiLab register being written and failed read back validation

- Fixed: on rev D+, INIT\_LP\_CLOSE\_HO[\_PLLx] configuration bit is now set to 1 when either ramped exit from holdover option is selected in CBPro DSPLL Configure page. Previously, it would have been 0. Without this setting, if the DSPLL first initializes with no input clocks, enters free run, and later an input is available, the DSPLL will not ramp when exiting free run.

- Fixed: if you wrote a design from the CBPro wizard without EVB GUI open, launched the EVB GUI, and then ran the power measurement compare, it complain saying must write project.

- Remove ID settings refresh button from field programmer EVB GUI; use scan instead

- On rev D+, support 1/16 ppm resolution on precision OOF thresholds through writing of OOFx\_CLR\_THR\_EXT,

OOFx\_TRG\_THR\_EXT settings

- Add text to gapped clock tooltip: "A valid gapped clock must have a minimum frequency and clock cycle density

as specified in the datasheet."

- Raise Fpfd(min) when Zero Delay Mode is enabled from 64k to 128k

- OOF improvements:

- Editor enforces that OOF clear threshold must be <= trigger threshold</li>

- New DRC error if OOF clear threshold must is > trigger threshold; therefore existing projects that violate new editor rules will be flagged with error

- Only include N\_FSTEP\_MSK in exports/reports on devices that do DCO on Nx (40/41/42/44/45, not 42H/44H).

- Improve Zero Delay Mode (ZDM) phase alignment at low PFD frequencies by changing how loop gain coefficients are calculated

- DUT Dump feature in EVB GUI supported in field programmer again

### CBProSi534x8xFOTF CLI:

- Fixed: the tool ignored the plan(s) for N4 divider. I.e. the --plans-n4 option was being ignored.

- For Si5340/41/42/42H/44/44H/45, the frequency planner in FOTF mode now optimizes for lowest jitter even if that means that no single N divider is integer.

Updates for pre-release devices.

Version 2.16.1 [ 2017-07-19 ]

# Si538x/4x

Fixed: when creating a new Si5348/83/84 design, IN3/4 CMOS only inputs were auto assigned to DSPLL A&C; these inputs are DSPLLD only

Version 2.16 [ 2017-07-18 ]

#### Si535x

Fixed: Incorrect pin mux configuration for Si5351A

# Si538x/4x

Si5340/41/46/47 Stuck Divider Fix:

- During power up or upon hard reset, some Si5340/41/46/47 devices may, on rare occasion, see an unusual clock divider failure resulting in output clocks not being generated. Once a device has successfully generated clock outputs, they will continue running without issue. Although the failure mechanism is random, Silicon Labs has not observed successive failures in tests run over many parts. Silicon Labs has observed that in several devices cycled with a hard reset more than a million times, output clock failure rates can be seen in rare instances (a few hundred times). Multiple workarounds in case of clocks not being generated have been identified and are detailed below.

- Fix: Orderable Part Numbers (OPNs) created by CBPro 2.15.6+ will have a baseline register changes to address the issue

- Fix: Register script exports generated by CBPro (wizard,CLIs) have fix via update to programming preamble

Si5342/42H/44/44H/45/46/47/48/83 Precision & Fast OOF Disabled Exit From Holdover Fix:

- If <u>both</u> precision and fast OOF were disabled for an input clock and holdover history was valid the device, exit from holdover would not occur on clock recovery

- Example sequence showing issue:

Lock the device all is OK

Remove the clock

all is OK; OOF, LOS and LOL are all asserted

Put the input clock back

OOF, LOS, HOFRB are negated, LOL is asserted, the input

and output are not locked

Issue a soft reset all is OK

Fix: if both precision and fast OOF were disabled, CBPro now:

- Sets OOF\_CLK\_DIS[in] and OOF\_DIV\_CLK\_DIS[in] to 1 if input is not enabled (change)

- Sets OOF\_ON\_LOS[in] if input is not enabled OR precision OOF is enabled OR fast OOF is enabled (new setting; change so that device does not assert OOF with LOS)

### Si5342H/44H N PIBYP Fix:

- When DCO mode was enabled and N0 divider was integer, N\_PIBYP[0] would have the wrong value.

- If DCO mode was enabled, NO divider was integer, and N\_PIBYP[x] was incorrectly set, then frequency plans approaching the upper frequency limit could yield no output clock.

- Fix: N PIBYP[x] set to 1 if Nx is integer and 0 if Nx is fractional.

# Other Bug Fixes:

- Fixed: OUT1\_DIV2\_BYP (Si5342H/44H) and OUT3\_DIV2\_BYP (Si5344H) were not included in design reports and settings exports; the correct values were reflected in register exports and NVM images, however, so no customer configuration issues

- Fixed: Si5342H/44H: was not always supporting R bypass for high speed outputs when manually assigned to an N divider

- Fixed: Si5383/84: if the project used fixed host I2C address mode, the address was not editable until mode was toggled

- Fix rare crash when close NVM burn tool window

#### Misc:

- Si5340/41/42/44/45 Rev D: Nx\_HIGH\_FREQ bit is now set if a MultiSynth (Nx) divider value is less than 10. This bit is in 0x0A14[3], 0x0A1A[3], 0x0A20[3], 0x0A26[3], and 0x0A2C[3]. This improves clock stability for high MultiSynth frequencies.

- Changed the default ramping for new designs to ramped exit from holdover only. This is the recommended setting when switching between input clocks that differ in frequency by less than 10 ppm. The text has been improved for available options.

- Rev D: new checkbox on PLL page to enable or disable preserve holdover history. This controls the HOLD\_PRESERVE\_HIST[\_PLLx] setting. Preserve holdover history should be turned OFF if clock switching between two input clock that are different in frequency by more than 10 ppm.

- Improved spur avoidance in frequency planner.

- New LOS threshold "set for me mode". This is the default for new designs. Silicon Labs recommends checking this when hitless switching is enabled to ensure optimal performance.

- Miscellaneous Design Rule Check (DRC) changes

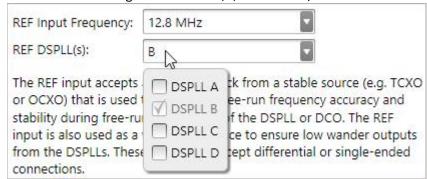

- REF can now be assigned to DSPLL A,C,D on Si5348/83

- GRADE, PKG\_ID, OPN\_IDx, and OPN\_REVISION are now included in datasheet addendums, matching the value programmed on the device at the factory.

- Updates for pre-release devices

# Version 2.15 [ 2017-05-12 ]

#### Si535x:

- Fixed: OE control was not being cleared when exporting

- Fixed: Outputs where being powered down when selecting Disabled

- Fixed: No solution plan was showing as empty plan in design report instead of displaying error.

### Si538x/4x:

- Si5348/83/84: show DSPLL B(REF) options (bandwidth)

- Si5383/84:

- Fixed: Fout(max)=33.554432MHz on OUT6 when OUT5=1Hz was not being enforced; would allow entry, but any real/virtual DUT write such as orderable part number creation, register export, or EVB write would generate error due to R divider range being exceeded

- o Power estimate improvements

### ClockBuilder Pro Field Programmer:

- CBProDeviceWrite, CBProDeviceRead Command Line Tools (CLI)

- New: supports in-socket read/write

- New: supports Si5383/84 via the new --family argument (--family si538x4x or -family si538x4xfw)

- The --family argument is now <u>required</u> when targeting a PCB via I2C or SPI serial connection except for CBProDeviceWrite --project mode (family can be inferred in this use case)

- CBProSi534x8xFirmwareDownload CLI now supports the field programmer in socket mode

- NVM Programming Tool:

- Now supports Si5383/84 flash programming, in-socket or in-system (wired to PCB)

- The button to launch the tool on the welcome screen, previously labeled "NVM Burn Tool", is now labeled "NVM Program Tool"

- o Improvements for other Si538x/4x (non-firmware) devices:

- Reporting of full part number of detected device

- Explicit design rule check results performed on project selection

- Improved organization/layout

- The EVB GUI now supports the Si5383/84 via field programmer, using new LGA56 field programmer socket or insystem (wired to PCB)

- The CBPro wizard now supports in-socket or in-system (wired to PCB) write to DUT; previously the dashboard forced the field programmer to assume wire mode

#### Version 2.14 [ 2017-04-21 ]

#### General:

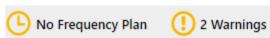

• You can now create "no plan" projects when a device supports in-system programming. For example, on Si5351A and Si5345 you don't have to define an input or an output to create an OPN or export the design. DRC warnings are generated instead of errors.

• The OPN wizard now requires you to review any DRC warnings present and acknowledge them by clicking a checkbox before continuing:

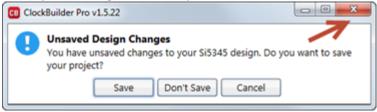

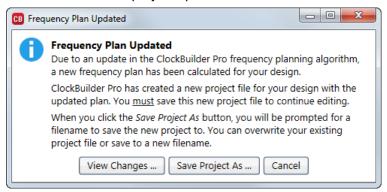

- Fixed rare error "cannot set Owner property to a Window that has not been shown previously" when opening project with frequency plan change

- When exporting file from dashboard, device revision is included in the default filename

- Updates for pre-release devices

#### Si535x:

- Fix bug where the pin mux mapping between CO/C1 and P1/P2 was switched for Si5350B/C

- Improved frequency planner to allow the use of both PLLs when it cannot find a solution and all outputs share the same feature

### Si538x/4x Register Export Improvements:

- Improved programming reliability for the following conditions:

- Writing a configuration script too slowly can cause a faulty VCO calibration that may trigger a LOL signal (Si5342/44/45/48, Si5342H/44H, and all Si538x) operating over temperature.

- If a new configuration is loaded within 300 msec of reset or within 300 msec of loading a previous configuration, the device may still be running its calibration sequence, possibly leading to a faulty VCO calibration that may trigger a LOL signal.

- The changes described below ensures programming functions as intended under all conditions regardless of how slowly the configuration script is written or how recently another configuration has been loaded.

- Register export changes:

- o Si5342/44/45/48, Si5342H/44H, and all Si538x: added register 0x0540 writes to preamble/postamble

- All devices: added 300 msec delay after preamble to export scripts and real DUT writes for all devices (i.e. done on EVB and field programmer). In export scripts the delay is added as a comment.

- Added comment blocks to register export scripts breaking preamble, configuration, and postamble into sections

- Example of new export script:

```

# Start configuration preamble

0x0B24,0xC0

0x0B25,0x00

0x0540,0x01

# End configuration preamble

#

# Delay 300 msec

# Delay is worst case time for device to complete any calibration

# that is running due to device state change previous to this script

# being processed.

#

# Start configuration registers

0x000B,0x68

```

```

0x0016,0x02

...

0x0B57,0x0E

0x0B58,0x01

# End configuration registers

#

# Start configuration postamble

0x0514,0x01

0x001C,0x01

0x0540,0x00

0x0B24,0xC3

0x0B25,0x02

# End configuration postamble

```

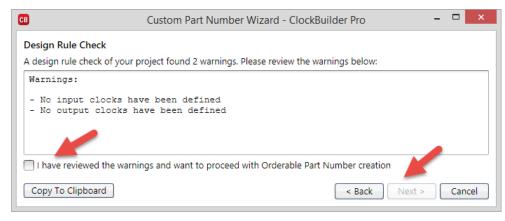

- New "Si538x/4x Register Export Upgrade Tool" is available to add 0x0540 write, delay comment, and section comments to an existing register export

- CSV and C header file files supported

- Launched from Start Menu:

Does in place edit, creating backup of original

#### Si5348/83/84:

- 83/84: Fixed: an N divider could be selected outside the restricted DCO range in 1pps mode; you would get a plan check DRC error if this occurred

- 83/84: Fout(max) now set to 685 MHz on DSPLL D if 1pps input mode

- 83/84: rapid lock calculation update

- Si5383 sample design updated: DSPLLA and C set to 10Hz with 100 Hz fastlock

- Si5384 sample design added

- All: changed default nominal and fastlock bandwidth for new designs on DSPLL A/C/D from 100/1k to 10/100 Hz

- All: new DRC when DSPLL A, B, or D bandwidth is >= DSPLLB bandwidth. Example:

Because DSPLL A, C bandwidth is equal to or higher than DSPLL B bandwidth, the stable clock connected to the

REF input will not be used as a jitter / wander reference for DSPLL A, C. It will, however, continue to function as

the free run / holdover reference.

### Si538x/4x Misc:

- Fixed: could not load very early (old) Si5348 project files that did not use all PLLs

- Fixed: if Zero Delay Mode (ZDM) was enabled, the planner could place even common multiple related outputs on the ZDM divider even though the divider range could not support this, leading to confusing planner error. For example, if the ZDM output was 64kHz and there was a 400 MHz output, the planner would try to put these both on NO even though the N divider range would not support this.

- Don't add hitless switching performance DRC if only 1 input clock on PLL

- Improved silab bank burn sequence used by I2C Address Burn tool

- File->Write Register File now detects "Delay XXX" comments in register file and pauses, where XXX is in milliseconds. For example:

- # Delay 100 or

- # Delay 100 msec

# Version 2.13.0.1 [ 2017-03-27 ]

### Si535x:

• Fixed: bug where the pin mux mapping between CO/C1/C2 and PO/P1/P2 was switched for Si5350B/C

# Version 2.13 [ 2017-03-03 ]

Add support for Si5383/84, a network synchronizer supporting 1 PPS to 750 MHz inputs.

Export Improvements (All I2C/SPI Configurable Devices):

- Fixed: the multi-project export GUI was not creating per-project register write scripts and setting dumps

- Added a copy project option to multi-project export GUI and CLI. For example, if you do multi-project export on 4 project files, P1-Project.slabtimeproj through P4-Project.slabtimeproj will be created.

- Added option to create C code register config scripts to the multi-project export GUI (this was already in the CBProMultiProjectExport CLI).

- Multi-project export now handles projects that write different settings. If a register is not written (not defined and a don't care) by one project but is defined by another, the value cell will be empty for the project(s) that do not define the register. These empty cells will not count towards the Varies computation. Previously multi-project export would fail with an error under these conditions.

- Multi-project export now creates delta register write scripts in addition to full configuration scripts for each

project, similar to what the CBProSi534x8xFOTF CLI creates. Each delta script includes the programming preamble sequence, the register writes that vary between any one project, and the post-amble sequence. This

provides a more efficient way to switch between configurations using the following workflow:

- Device power up or reset

- Write a full configuration write script (P\*-Registers-Script.txt)

- Write any delta update configuration write script (P\*-Registers-Script-Delta-Only.txt)

All multi-project export samples, user manuals, and the training presentation bundled with CBPro have been updated to discuss this.

Updated the CLI user guide, in-system programming overview, and samples to reflect these changes.

### Si538x/4x:

- New frequency planner priority page added to wizard for Si5340/41/42/42H/44/44H/45 projects

- Allows you to select an output to be lowest jitter and guaranteed to be placed on an integer MultiSynth:

Maximize the number of low jitter outputs CBPro will select the frequency plan with the most number of outputs on an integer N divider.

# Select one output as lowest jitter

CBPro will ensure that the selected output is on an integer N divider. Where possible, other outputs that are even common multiple related will be placed on the same divider, within the bounds of any manual N divider assignment you have configured.

Output: OUT5

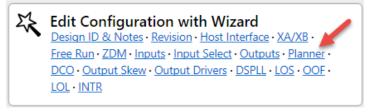

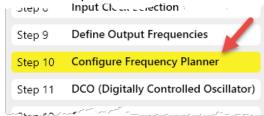

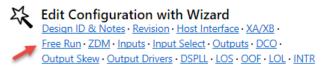

Getting to the new page from the dashboard:

From the step menu:

- Changed the threshold for "hitless switching performance may not meet datasheet specification due to Fpfd less than XXX" DRC from 64kHz to 1MHz

- Si5348: removed OLB\_HO\_FORCE (and associated FIXREGS) from design report, exports: never needs to be written on PLLB since free run only mode is not supported on PLLB

- NVM burn tool improved:

- Now reports on:

- CBPro version that created the project file

- A unique hash (similar to a checksum) for the user NVM bytes that will be burned. This is useful to create a fingerprint of a project's resulting device configuration.

- Cumulative # good/bad burns since the tool was launched

- If the project file has a DRC error or other error, this is now immediately reported on instead of having to wait until the "Burn NVM" button is pressed

- EVB sample projects updated for Si5341/46/47

#### Misc:

- EVB GUI no longer does device reset detection polling when the SPI, I2C, or register editor tabs are selected

- Updates for pre-release devices

# Version 2.12.1 [ 2016-12-15 ]

#### Si538x/4x:

• Fixed: The EVB GUI status registers were not properly customized for the target device when using the CBPro Field Programmer.

# Version 2.12 [ 2016-12-12 ]

#### Si5350/51 Support Added:

- Detects and controls an Si5350/51 Evaluation Board (Si535X-B20QFN-EVB). EVB control is not supported on Windows XP.

- Can create a factory programmed part (Orderable Part Number)

- Can export an Si5351 configuration for in-system programming using I2C

#### Si538x/4x:

- Fixed: 1 Hz outputs on Si5348 could be relocated by the clock placement wizard. Also, it might relocate the related cascade output or assign an output to the cascade if it was not being used.

- Fixed CBProProjectEdit, CBProMultiEditAndExport, CBProSi534x8xFOTF CLI bugs:

- Bandwidth value in m (milli) were being mapped to M (mega). CBPro now strictly treats bandwidth m as

1e-3 in edit files. In clock frequency edits, m continues to map to 1e6.

- Setting a clock to Disabled was not working

- Fixed: Fvco was not always constant in Si5347 FOTF, causing Nx divider value written for a plan to be off

- Fixed: on Si538x/4x, CBProDeviceWrite CLI in --project mode was always setting IO\_VDD\_SEL to 1 when writing to a DUT via the field programmer, ignoring the setting in project file; this would cause errors when writing a project with I/O Power Supply option set to VDD(Core)

- Fixed: DSPLL holdover timing text was clipped on rev D

- The Si5340/41/42/42H/44/44H/45 frequency planner further optimizes for reduced jitter by optimizing the values of fractional N dividers

- New DRC warning on Si5340/41/42/44/45 if the DCO range is greater than 350 ppm

#### New CBProDeviceRead Command Line Tool:

- Reads device registers and associated named settings (aka bitfields) from an EVB or the CBPro Field Programmer (FP). Has three modes of operation:

- Read one or more named settings you specify on the command line (--settings option). Reads are done

at the register level, but output is per-setting.

- Read one or more registers you specify either on the command line (--registers option). In this mode, no mapping to setting names is done: you get back a simple register address, value list.

- Read all read-only and read-write settings on the device (--all option). Reads are done at the register level, but output is per-setting.

- Supports Si538x/4x, Si535x, and Si512xx EVBs. Field programmer support is currently limited to Si538x/4x devices.

- Examples:

C:\> CBProDeviceRead.exe --quiet --settings PN\_BASE DEVICE\_REV

| Location     | Type | Setting Name | Decimal Value | Hex Value |

|--------------|------|--------------|---------------|-----------|

|              |      |              |               |           |

| 0x0002[15:0] | R/O  | PN_BASE      | 21317         | 0x5345    |

| 0x0005[7:0]  | R/O  | DEVICE_REV   | 3             | 0x03      |

```

C:\> CBProDeviceRead --all --quiet --format csv

Location, Type, SettingName, DecimalValue, HexValue

0x0000[3:0],R/O,DIE REV,5,0x5

0x0002[15:0],R/O,PN BASE,21317,0x5345

0x0004[7:0],R/O,GRADE,0,0x00

0x0005[7:0],R/O,DEVICE REV,3,0x03

0x0B4A[4:0], R/W, N CLK DIS, 0, 0x00

0x0B57[11:0],R/W,VCO RESET CALCODE,270,0x10E

C:\> CBProDeviceRead.exe --quiet --registers 0x0002 0x0003 0x0005

Address Decimal Value Hex Value

_______

0x0002 69

0x45

0x0003 83

0x53

0x0005 3

0x03

```

#### Misc:

- Updated in-system programming training available on the Welcome screen

- Updates for pre-release devices

### Version 2.11.1 [ 2016-10-26 ]

Fixed: on Windows XP, project files could not be opened.

# Version 2.11 [ 2016-10-24 ]

### General Changes

# Command Line Tools:

- New CLI, CBProMultiEditAndExport, that combines the features of CBProProjectEdit and CBProMultiProjectExport into a single tool:

- You define a base project file

- You define alternate clock configurations in the form of simple text file(s) (like FOTF tool)

- You run this tool to create new (edited) project files and export files for both the base project file and created project files

- o Unlike FOTF tool, the frequency plan for each is independently solved

- So this helps automate creating clock variations of a project in situations where the FOTF tool does not make sense – such as wanting optimal Fvco for each plan -- or is not supported (Si535x, Si5348, etc)

- More and improved CLI samples in C:\Program Files (x86)\Silicon Laboratories\ClockBuilder Pro\CLI\Samples

- The individual user guides for each CLI are also now copied to <a href="C:\Program Files (x86)\Silicon">C:\Program Files (x86)\Silicon</a> Laboratories\ClockBuilder Pro\CLI\Docs

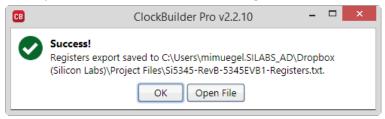

- Brand new training deck, *CBPro Tools & Support for In-System Programming*, walks through common in-system programming scenarios/workflows and provides an overview of related tools

- Updated the CLI user manual

- Both are available through on CBPro Welcome screen and the Windows Start Menu

#### Misc:

- Don't allow draft datasheet addendum to be created if there are DRC errors

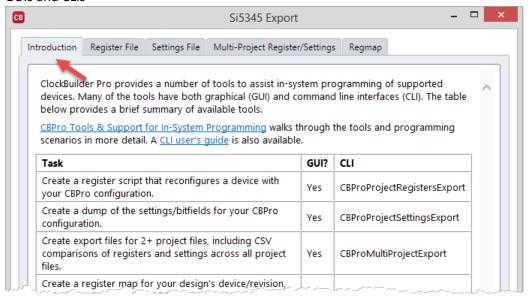

- The Export GUI now has an intro tab that is customized to the current part. It briefly describes available export GUIs and CLIs

Updates for pre-release devices

### Si538x/4x Family Changes

#### Misc:

- Fixed: if a clock frequency expression had an error and the clock was then marked Unused, further edits to unrelated clocks might not be accepted

- CBPro no longer allows an unconfigured clock to be used in a frequency expression

- Si5380: added 921.6, 460.8, 230.4, and 115.2 MHz to supported output frequency list

- GRADE (0x0004[7:0]) & TOOL\_VERSION (0x0006[23:0]) DUT settings are no longer included in rev D register and settings exports; these are read only

#### Command Line Tools:

- Fixed: CBPro device write and firmware download CLIs CBProDeviceWrite.exe and CBProSi534x8xFirmwareDownload did not parse --io-voltage decimal in US-centric mode on non-US systems, causing disconnect to user manual

- CBProSi534x8xFOTF CLI:

- Fixed: tool would fail on 40/41/42/42H/44/44H/45/80 if an output had been manually assigned to an N divider and then set to Unused

- 41/45 mode now forces N\_PIBYP[x] bit to 0 in base config and register script if an N divider is doing FOTF. This ensures that N\_PIBYP remains fixed across the base and all plan scripts (and is therefore not included in any plan scripts)

- Project edit and FOTF plan files can now specify HOBW to update exit from holdover bandwidth; this is required

if OLBW has been specified and ramping has been disabled

### **EVB GUI:**

- Improved memory footprint by decreasing the number of log message lines that are cached; this should speed up EVB GUI on most systems

- Suspend status register polling during project file, register file, and setting file writes to EVB

# Version 2.10 [ 2016-09-07 ]

# General Changes

# Bug Fixes:

- Fixed: in datasheet addendums PDF files, the Ω character was a blob of text

- Fixed: the step pulldown menu in the wizard had "(A)" after every step

### New CBProDeviceWrite Command Line Tool (CLI):

- Writes a project file, settings file, or registers file to a supported EVB

- Writes to a system board using the <u>ClockBuilder Field Programmer</u> via I2C or SPI

- Same effect as the EVB GUI File menu "Write XXX" tools

- Help available via CBProDeviceWrite --help

#### Misc:

- Change addr[x:y] bitfield callouts to little endian ordered msb:lsb. For example, 0x0302[43:0] for Si538x/4x N0\_NUM.

- Text in design report and frequency plan windows can now be selected

- Allow trailing // and # comments in setting and register files that can be written using the EVB GUI or CBProEVBWrite CLI. Example:

DESIGN\_ID0,65 # Decimal value (ASCII 'A')

0x026B,0x41 // DESIGN\_ID0 = 'A'

### Si538x/4x Family Changes

# **Bug Fixes:**

- Fixed: frequency ranges in rev B output editor and rev D device grade section of design reports were incorrect on Si5340/41/42/44/45

- Fixed: Fout(min) for LVCMOS outputs for all revisions changed from 1kHz to 100Hz to match datasheet

### LOS Enable Changes:

- An issue exists where a loss of input signal can cause an inadvertent DSPLL recalibration when LOS is disabled. During the recalibration sequence, a loss of output clocks from the DSPLL occurs.

- As of this release, LOS can no longer be disabled.

- If a project file is opened that has LOS disabled, you will be notified and LOS will be re-enabled.

#### New Hitless Switching Restrictions/Warnings:

- Zero Delay Mode (ZDM) and hitless switching results in conflicting behavior. As of this release, ZDM and hitless switching can no longer be used together.

- New DRC warning if automatic clock selection is enabled, hitless switching is enabled, and a PFD frequency is less than 64 kHz: hitless switching performance is reduced in this scenario.

#### Misc:

- On Si5348, set PFD\_TRIM\_PLLx for any DSPLL not in free run only mode

- Better Fdco selection on 47-like DSPLLs on rev D for certain designs

- VDD voltage can no longer be changed in EVB GUI; it is forced to 1.8V

- Updates for pre-release devices

# Version 2.9 [ 2016-7-29 ]

### Si538x/4x Family Changes

# Support Si538x/4x Revision D:

- This is the default revision for new designs

- Note you will no longer be able to create a revision B custom part number (aka OPN) without the assistance of Silicon Labs

- While you will no longer be able to create revision B custom part numbers, you can still open and edit revision B

project files, and create new in-system programming exports incorporating the enhancements included in this

CBPro release

# New Free Run Only Mode:

- The device can now be configured to operate in free run mode. The DSPLL will operate like a clock generator in free run mode, locking to the crystal (or XO) on XA/XB

- Supported on Si5342/42H/44/44H/45/46/47/48/80

- Available on a per-DSPLL basis on Si5346/47/48

- FORCE HOLD, FIXREGSAx, and FIXREGSDx register settings defined to support this feature

- Select via step menu or dashboard:

# FOTF CLI Improved (CBProSi534x8xFOTF.exe):

- Now supports Si5340/41/42/42H/44/44H/45/80 in addition to the Si5346/47:

- o Requires you to manually assign outputs to a specific N divider

- Alternate plans are specified on a per-N divider basis

- Searches all desired plans for optimal Fvco

- Creates simple register write scripts to switch a single N divider from one plan to another

- Example included with CBPro (C:\Program Files (x86)\Silicon Laboratories\ClockBuilder Pro\CLI\Samples\Single-PLL-FOTF)

- Example added for Si5347 (C:\Program Files (x86)\Silicon Laboratories\ClockBuilder Pro\CLI\Samples\Multi-PLL-FOTF)

- Improved the user manual available via the --help option

### Misc:

- Improvements to frequency planner, resulting in lower output jitter for many designs.

- New DCO Design Rule Checks (DRCs) to warn if FINC/FDEC could go beyond output frequency range

- New FIXREGSAx and FIXREGSDx register settings are included in design reports, setting exports, and register exports. These settings are NVM backed and define register address/data sequence to restore on NVM reload (such as at device reset). With FIXREGS, a DUT register that is normally not NVM backed can be essentially be made NVM backed. CBPro uses these to set the FORCE\_HOLD setting in free run only mode on Si5342/42H/44/44H/45/46/47/48/80 and OUTERLOOP\_DIS on Si5342H/44H based on DCO enable state. Additional FIXREGS are included in Si5346/47 to support certain factory only features.

- Improved support for pre-production devices

# Bug Fixes:

- Fixed: on Si5348, DSPLL LOL gain factor could be miscalculated on DSPLL A/C/D

- Fixed: CBProSi534x8xFOTF command line tool would fail to export if an output had been assigned to a DSPLL previously, and then is marked Unused

- Fixed: 41/45 DCO report mislabeled Nx\_DEN as Nx\_NUM

- Fixed: if an existing project is opened that has unsupported output driver mode selected due to Fout >= 1.5 GHz, fixing the mode would not always cause the frequency planner to re-run.

#### Si5121x Family Changes

Changed maximum input frequency from 166 MHz to 165 MHz

# Version 2.8 [ 2016-4-24 ]

Add support for Si5342H and Si5344H. These are 2- and 4-output high frequency, ultra-low jitter attenuating clocks with digitally controlled oscillators.

### Si538x/4x:

- Fixed: writing a project to the field programmer with a pre- production device would generate an error on 2nd or later writes

- Fixed: the first voltage measurement on an Evaluation Board after power up could be off significantly; this would normally surface as low VDD reading on "Read All"

- Improved support for pre-production devices

#### Si5121x:

- Update EVB user guide links

- Update pin editor to reflect that SSON input is active low

# Version 2.7.1 [ 2016-4-20 ]

Add Support for Si5121x Family of Clock Generators:

- Devices: Si51210, Si51211, Si51214, and Si51218

- EVBs: Si51211-EVB and Si51218-EVB

# Si538x/4x:

- Fixed: on single DSPLL parts, setting name for 0x0511[5:0] was FAST\_BW\_PLL instead of FAST\_BW3\_PLL; this

change affects design reports and setting exports

- Fixed: the clock placement wizard could crash if a frequency had never been entered on an output clock

- Adjust calculation of Fastlock Bandwidth coefficients in plans with low Fpfd (near 8kHz) to ensure LOL operates

properly when transitioning from Fastlock to phase lock. If affected by this change, when CBPro project file is

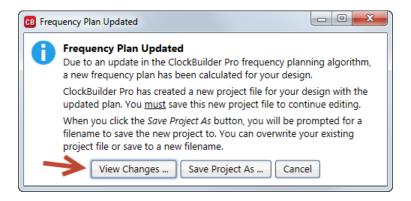

opened you will be notified of frequency plan change and be prompted to save your updated design to a project

file. Changes may occur to Fastlock bandwidth coefficient settings and LOL related DUT settings (registers).

- Added support for 46 ohm LVCMOS impedance @ 1.8V

- Increased 40/41 XO range from 120M to 200M

- Changed Si5340/41 LOS clear threshold default for new designs to 4, so that it passes the design rule check

- Improved XO-related documentation on XA/XB wizard page on Si5342/44/45/80

- Improved support for pre-production devices

# Version 2.6 [ 2016-3-29 ]

### Bug Fixes:

- Fixed: entering typo or other bad input for clock frequency would crash CBPro

- Fixed: the clock placement wizard did not take into account output names used in frequency expressions. After a

manual or automatic reorder, expressions were not adjusted and further editing would lead to unpredictable

results.

- Fixed: setting a GPO in the EVB GUI had no effect

- Fixed: frequency plan might not recalculate when an error in design was resolved and the plan was now out-of-date

- Fixed: in the power model to EVB comparison results, the VDD and VDDA measured values were swapped, leading to incorrect difference % listed

- Fixed: TOOL VERSION decode was wrong in EVB GUI's Info tab

- Fixed: on 41/45 variants, an integer M, fractional P solution might not be used in plan even when possible

#### New Phase Noise Measurement Service

- Provides a way you can request a custom phase noise report created by Silicon Labs support engineers in our lab – for one or more outputs in your Si538x/4x design.

- Click the link in the design dashboard Cloud Services section (lower left):

# Silicon Labs Cloud Services

You can <u>create a custom part number</u> for your design, which can be used to order factory pre-programmed devices. Or <u>request a phase noise report</u> for this design.

# Si538x/4x:

- Si5346/47/48: stop setting Mx\_NUM/Mx\_DEN and Nx\_NUM/Nx\_DEN to 1/1 left shifted when DSPLL is not used; also, stop setting FRACN\_CLK\_DIS\_PLLx to 1 in this case as it is a don't care

- Max output frequency support extended to 712.5M on Si5346/47 rev B

- Max output frequency support reduced to 711.5M on Si5348 rev B. If an output frequency between 711.5M and 712.5M is desired, contact Silicon Labs.

- Small changes to power estimation model

- Improved support for pre-production devices

#### Misc:

Export link removed from CBPro home page; open a project file and use the "Export" link on the design dashboard

# Version 2.5 [ 2016-2-23 ]

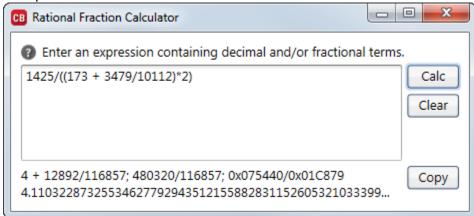

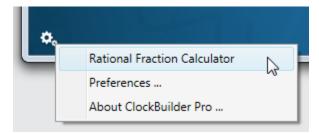

#### DCO:

- Additional detail added to all design reports, including Fout equations and all components used in the equation such as Fvco, Fpfd, and Rx

- Added similar detail to the Si5342H/44H DCO editor

- Fixed instructions clipping issue

- Made setting names in all Fout editor equations match the Family Reference Manual

# **Automatic Input Clock Switching:**

- No longer write input clock priority related settings when manual mode is used.

- Input clock priority no longer has a gap for un-assigned inputs

#### Misc:

- Fixed: on Si5348/83, LOS\_INTR\_MSK[3] and OOF\_INTR\_MSK[3] were always 1 and were not editable in CBPro, causing LOS and OOF on REF to never contribute to INTRb.

- Si5340/41: REFCLK\_EN, REFCLK\_CLK2PLL\_EN, and FRACNP\_CLK\_DIS are now optimized for case where INO-IN2 and IN3(ZDB\_IN) are not used.

- Improved support for pre-production devices

- Updated description of Si538x/4x Revertive Input Clock Select Mode

- Updated Target Holdover Exit Bandwidth label on DSPLL page

- Updated SPI 3-/4-wire descriptions

- Block Orderable Part Number creation (OPN) on Windows XP: not supported

# Version 2.4.0.3 [ 2016-1-8 ]

Digitally sign the USB drivers so they can be installed easily on Windows 10. Update CBPro installer digital signature to avoid publisher warnings.

# Version 2.4 [ 2015-12-8 ]

#### Misc:

- Fixed: DUT revision check was not being handled correctly with field programmer when writing design/project to volatile memory, giving incorrect error about revision mismatch

- Fixed: on Si5346/47/48, frac(Px) less than 5 could be permitted when non-zero ppm frequency offset workaround was enabled

- Fixed: opening very old project file (CBPro 0.7 and earlier) could crash CBPro

- Updates to EVB GUI "Create DUT Dump" tool (used to send device volatile and non-volatile configuration snapshot to Silicon Labs support personnel)

- Updates for pre-release devices

#### Si5348:

- Fixed: disabling non-zero ppm frequency offset did not affect MB divider search

- Fixed: Fvco was fixed value optimized for 48MHz XA/XB default, instead of varying based on XA/XB. This could

cause non-optimized dividers to be selected when using an XA/XB that is not the 48 MHz default.

- Change Fpfd(max) from 2M to 2.048M; this will raise Fpfd when IN3/4 is above 2 MHz, potentially improving performance.

# New Si5346/47 Frequency-On-The-Fly Command Line Tool:

- CBProSi534x8xFOTF.exe is the tool name

- This tool is used to define alternate output frequency plans for a supported device

- Tool output are register write scripts to load base config and switch to a single DSPLL to an alternate plan, plus various reports and support files

- Currently only Si5346/47 multi-PLL devices are supported

- Handles the requirement that Fpfd be fixed across frequency plans when a DSPLL shares an input of another DSPLL

- Type CBProSi534x8xF0TF.exe --help from a DOS prompt to review the user manual, including an example

The example described in the user guide can be downloaded from <a href="http://www.silabs.com/internal-apps-management/Timing/cbpro/Si538xFOTF-CLI-User-Manual-Example.zip">http://www.silabs.com/internal-apps-management/Timing/cbpro/Si538xFOTF-CLI-User-Manual-Example.zip</a> (the link is provided in the user guide)

CBProProjectEdit Command Line Tool Improvements:

- You can now edit DSPLL bandwidth

- Example for single DSPLL device:

OLBW,,100 Hz

FLBW,,1k

Example for multi-DSPLL device:

OLBW,,A,100

FLBW,,A,1k

OLBW,,B,200

FLBW,,B,2k

You can also specify bandwidth for multiple DSPLLs at once:

OLBW,,AB,100 Hz

FLBW,,AB,1 kHz

# Version 2.3.1 [ 2015-11-4 ]

Fixed: opening a very old CBPro project file, such as created before version 0.7, could crash the GUI.

# Version 2.3 [ 2015-10-26 ]

# **Bug Fixes:**

- Fixed: IN3/IN4 on Si5348 could erroneously trigger Px divider Design Rule violations

- Fixed: on 46/47/48, Fdco for PLLs that have the same single unique frequency might be different (for example, 100M,100M on A, 100M on C)

- Fixed: on Si5380, the EVB GUI Compare Design Estimates to Measurements tool would report 0 (zero) estimated current/power on VDDO0 and VDDO9 if only the "A" output was enabled (but the estimated total values were correct).

- Fixed: bad pin names on Si5348 output diagram

- Fixed: the Jitter Attenuator Clock Products link on CBPro home page was broken

#### Si5348:

- DSPLL B configuration page is now hidden in the wizard; there is no need to configure DSPLL B

- Default bandwidth settings for new designs and the EVB sample project changed to 100 Hz (open loop and Fastlock).

- New DRC if BW not 100 Hz on DSPLL B.

- Please contact Silicon Labs if your existing design uses a DSPLL B bandwidth that is not 100 Hz.

#### Misc:

- Fractional Px divider less than 5 will no longer be selected by the frequency planner

- Improvements and support for pre-release devices

# **Export Improvements & Additions:**

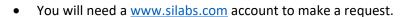

• New register map (aka regmap) tab in the GUI's export tool:

- This creates:

- o Regmap tables: CSV, text, and HTML regmap tables for the user's part+revision

- Regmap as C code: C code definition of the regmap

Where a regmap contains meta-data about each setting (register bit field) on a device, such as starting address and # bits for a setting

Example table (HTML shown; CSV and text versions also created):

| Setting<br>Name | Location     | Start<br>Address | Start<br>Bit | Num<br>Bits | NVM   | Type |

|-----------------|--------------|------------------|--------------|-------------|-------|------|

| DIE_REV         | 0x0000[0:3]  | 0x0000           | 0            | 4           | None  | R/O  |

| PAGE            | 0x0001[0:7]  | 0x0001           | 0            | 8           | None  | R/W  |

| PN_BASE         | 0x0002[0:15] | 0x0002           | 0            | 16          | SiLab | R/W  |

| GRADE           | 0x0004[0:7]  | 0x0004           | 0            | 8           | SiLab | R/W  |

|                 |              |                  |              |             |       |      |

# Example C header file:

```

#define SI5345_REVB_NUM_SETTINGS 373

#define SI5345_REVB_MAX_NUM_REGS 10

#define SLAB_NVMT_NONE 0

#define SLAB_NVMT_SLAB 1

#define SLAB_NVMT_CUST 2

#define CHAR char

#define UINT8 unsigned char

#define UINT16 unsigned int

```

```

typedef struct

CHAR* name; /* Setting/bitfield name

UINT8 read_only; /* 1 for read only setting/regs or 0 for read/write

UINT8 self_clearing; /* 1 for self clearing setting/registers or 0 otherwise

UINT8 nvm_type; /* 0 for not NVM backed; 1 for "silabs" bank; 2 for "user" bank

UINT8 bit_length; /* Number of bits in setting

UINT8 start_bit; /* Least significant bit of the setting

UINT8 reg_length; /* Number of registers that the setting is stored in

*/

*/

{\tt UINT16~addr[SI5345\_REVB\_MAX\_NUM\_REGS];} \quad /* \  \, {\tt Addresses} \  \, {\tt the} \  \, {\tt setting} \  \, {\tt is} \  \, {\tt contained} \  \, {\tt in}

UINT8 mask[SI5345_REVB_MAX_NUM_REGS];

/* Bitmask for each register containing the setting */

} si5345_revb_regmap_t;

si5345 revb regmap t const si5345 revb settings[SI5345 REVB NUM SETTINGS] =

/* DIE_REV */

{

"DIE_REV",

1, /* 1 = IS Read Only */

0, /* 0 = NOT Self Clearing */

SLAB_NVMT_NONE, /* Not stored in NVM */

4, /* 4 bits in this setting */

0, /* setting starts at b0 in first register */ \,

1, /* contained in 1 registers(s) */

{

0x0000, /* Register address 0 b7:0 */

},

{

0x0F, /* Register mask 0 */

}

},

}

/* Setting indexes into si5345_revb_settings array */

#define SI5345_REVB_DIE_REV 0

#define

SI5345_REVB_PAGE 1

#define

SI5345_REVB_PN_BASE 2

#define

SI5345_REVB_GRADE 3

#define

SI5345_REVB_DEVICE_REV 4

```

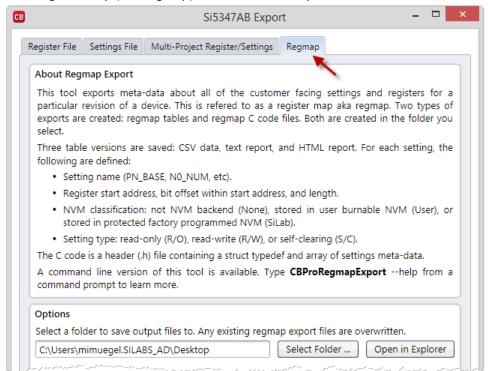

- New command line tool CBProRegmapExport.exe that does the same thing

- Register File export updated with new C code mode (similar to "Jump Start" option in other Silicon Labs Timing tools):

```

Options

Export Type:

Comma Separated Values (CSV) File